Xyloni開発キットでのPLLの使用方法

作成者:mou-mou

xyloni開発キットのチュートリアルではPLLについては記載がありませんでしたので、チュートリアルで作成したプロジェクトをベースにPLLを使用してみたいと思います。

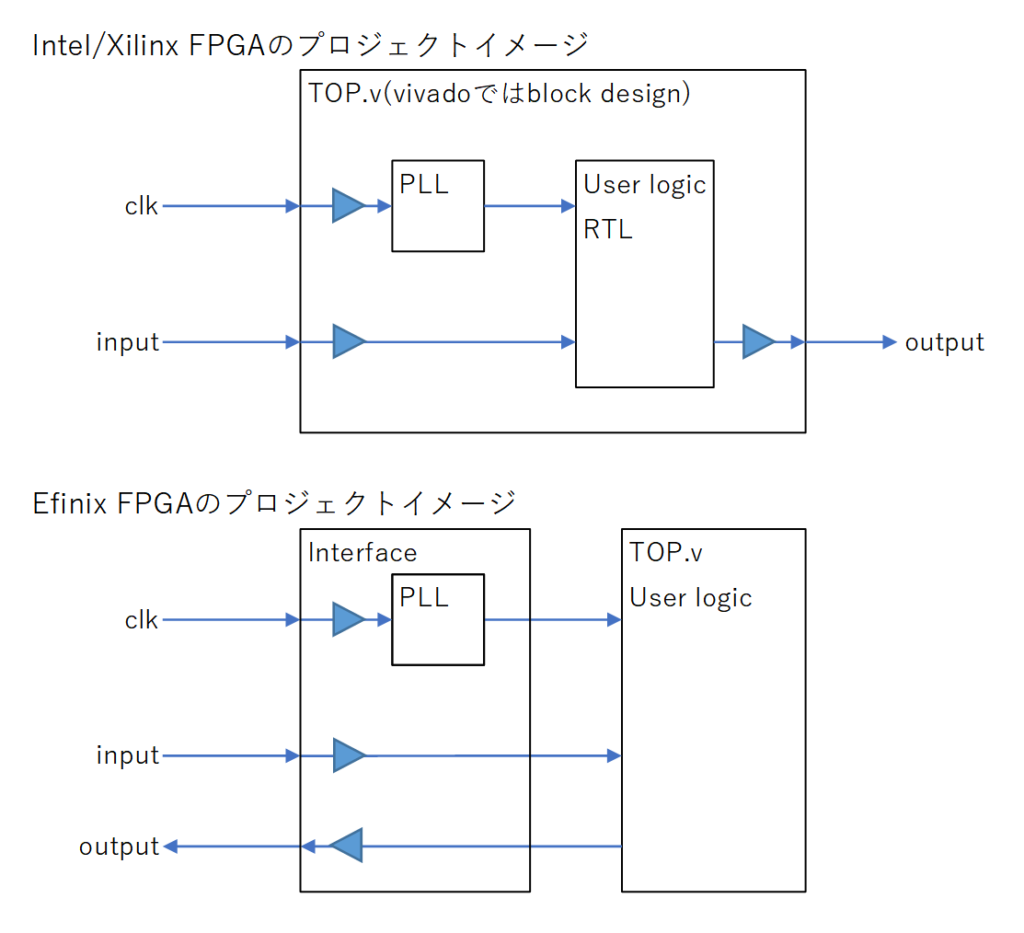

まず、概念的なところで、Intel等では、PLLはIPとして生成して、それをRTLの中に実装します。(Xilinx vivadoの場合は、Block Design上に置きます)

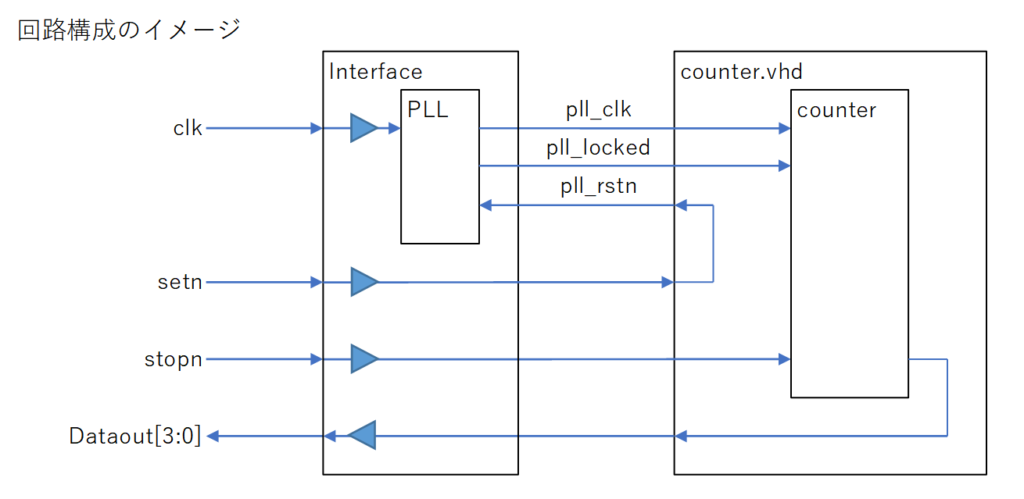

それに対して、Efinityの環境ではInterface DesignerでPLLを生成します。PLLはRTLの中に置かれるのではなく、Interfaceの中に存在して、InterfaceとRTLのTOP層が接続されるイメージとなっております。

では、以下の手順でプロジェクトにPLLを追加していきます。

Interface DesignerでPLLを追加

では、実際にxyloni開発キットのチュートリアルを最後までおこなったプロジェクトにPLLを追加してみます。

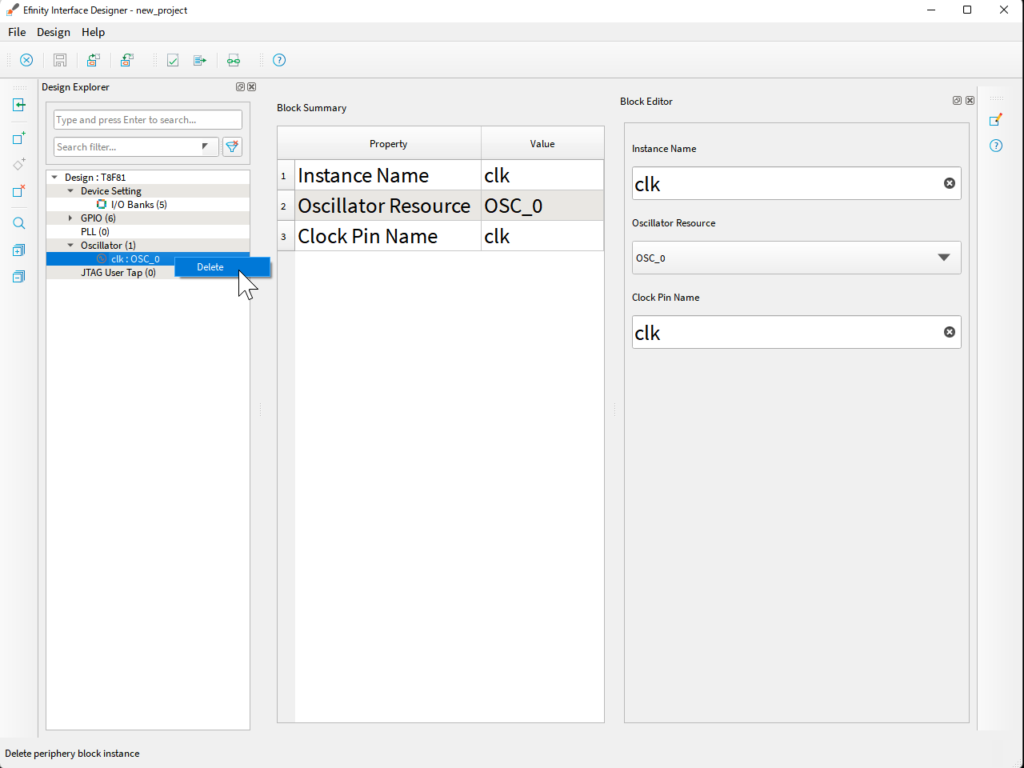

まず、Interface DesignerでOSCを削除します。

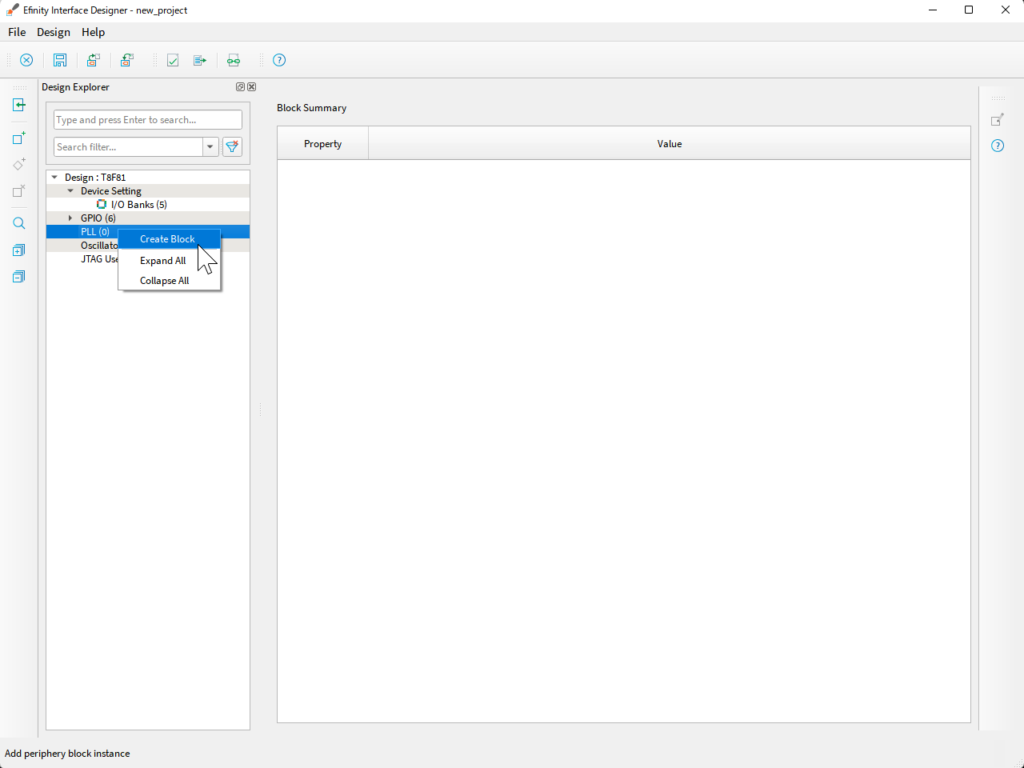

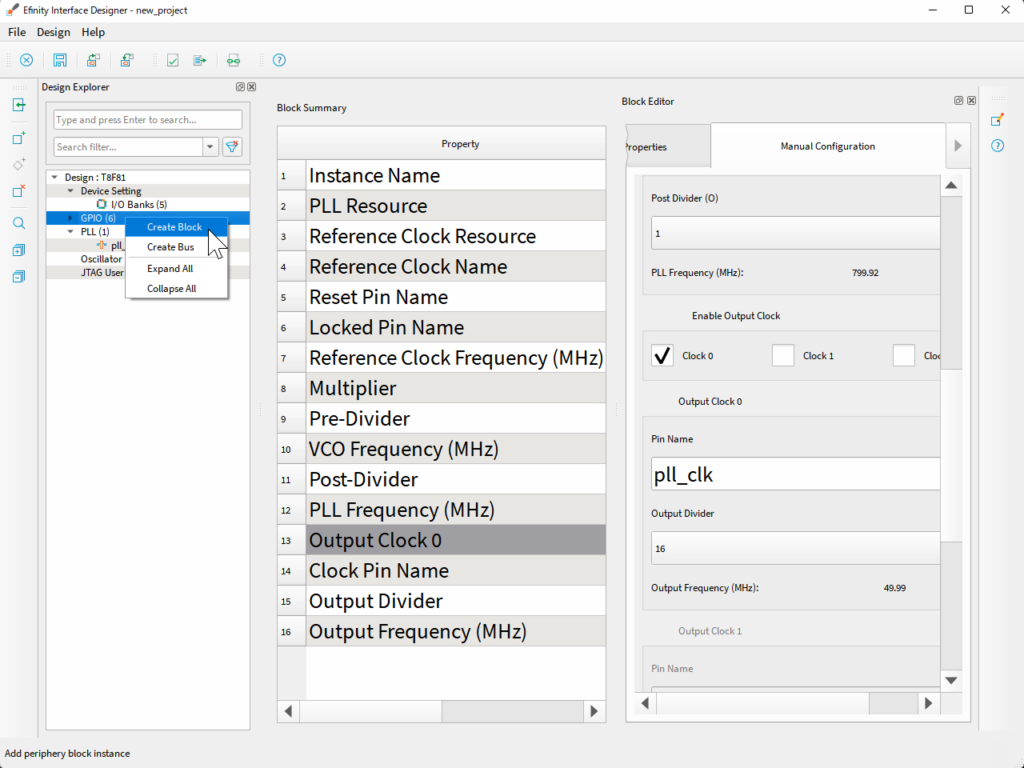

PLLを追加します。

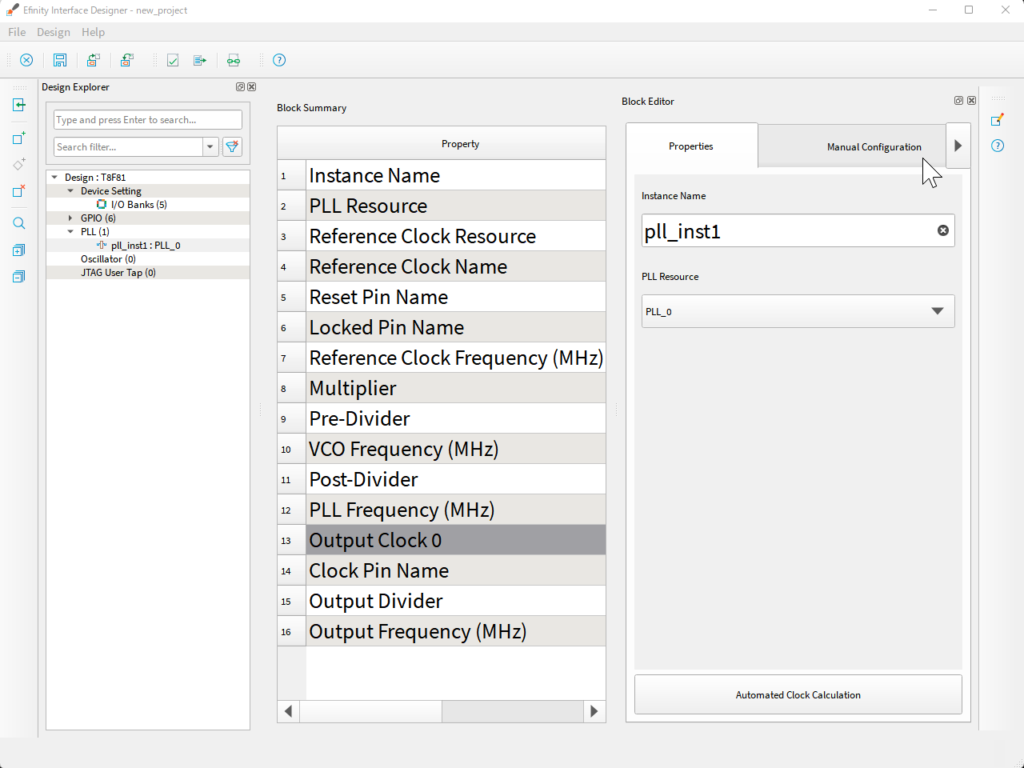

Manual Configrationタブに切り替えます。

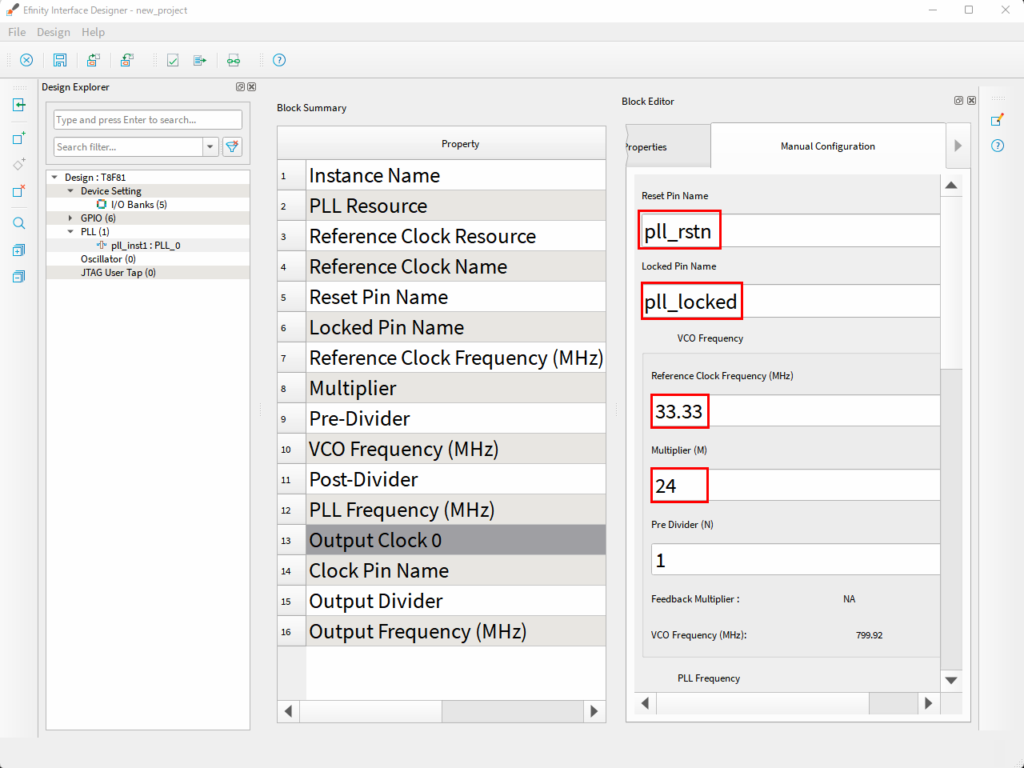

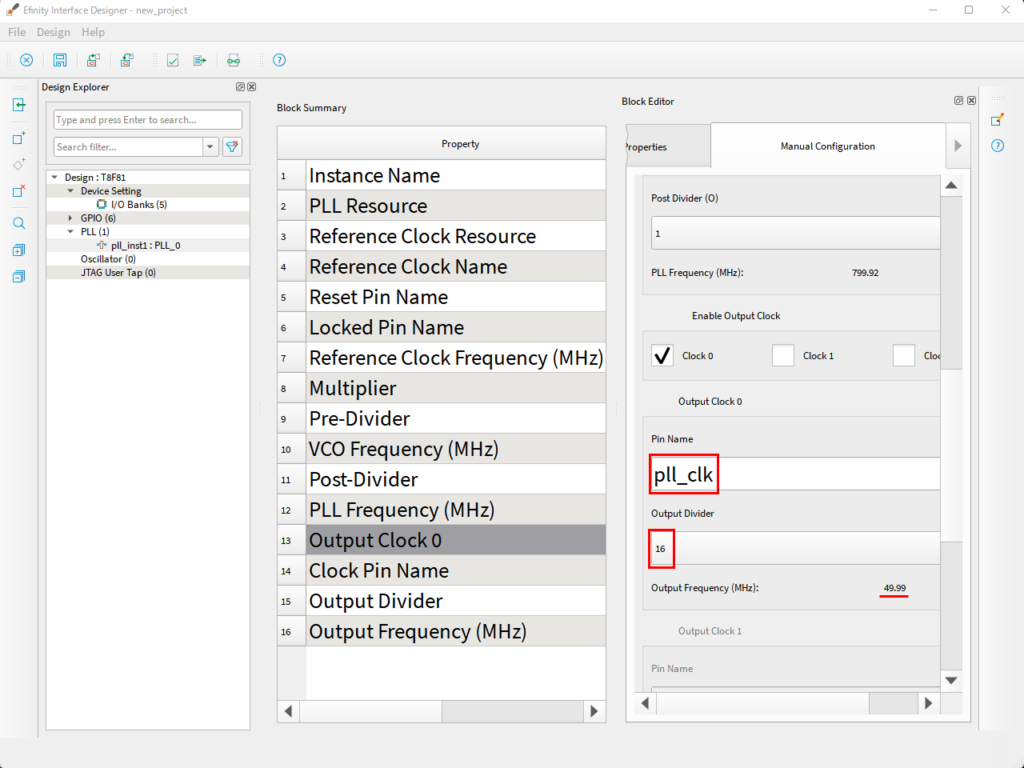

設定を入力していきます。33.33MHzをもとに50MHzのクロックを作ってみます。

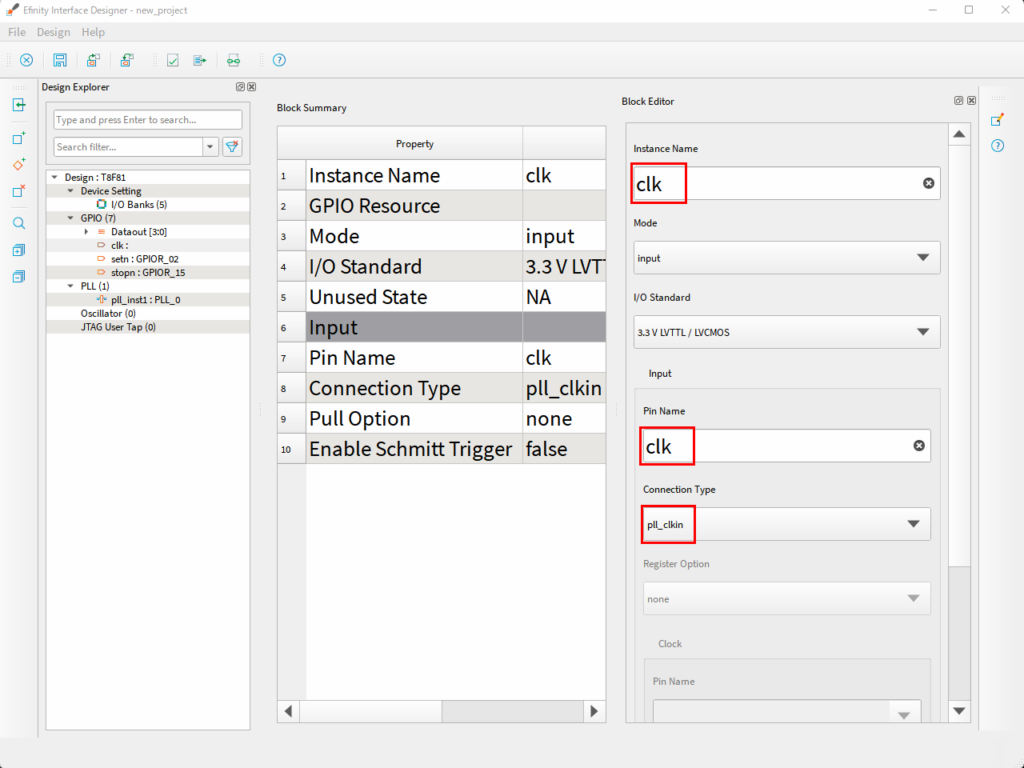

チュートリアルではInternal oscillatorを使用するために削除したGPIOのclkピンを復活させます。

Instance NameとPin Nameはチュートリアルのとき同じくclkとします。Connection Typeはpll_clkinとします。これで、このPINはPLLのクロック入力に接続されることになります。

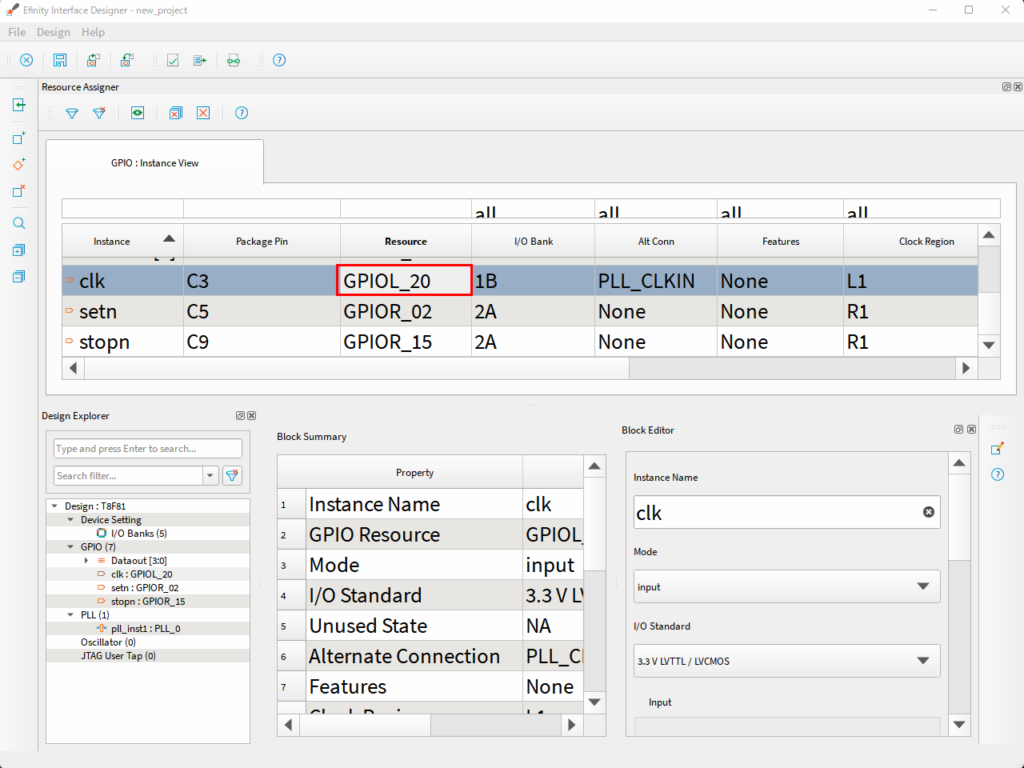

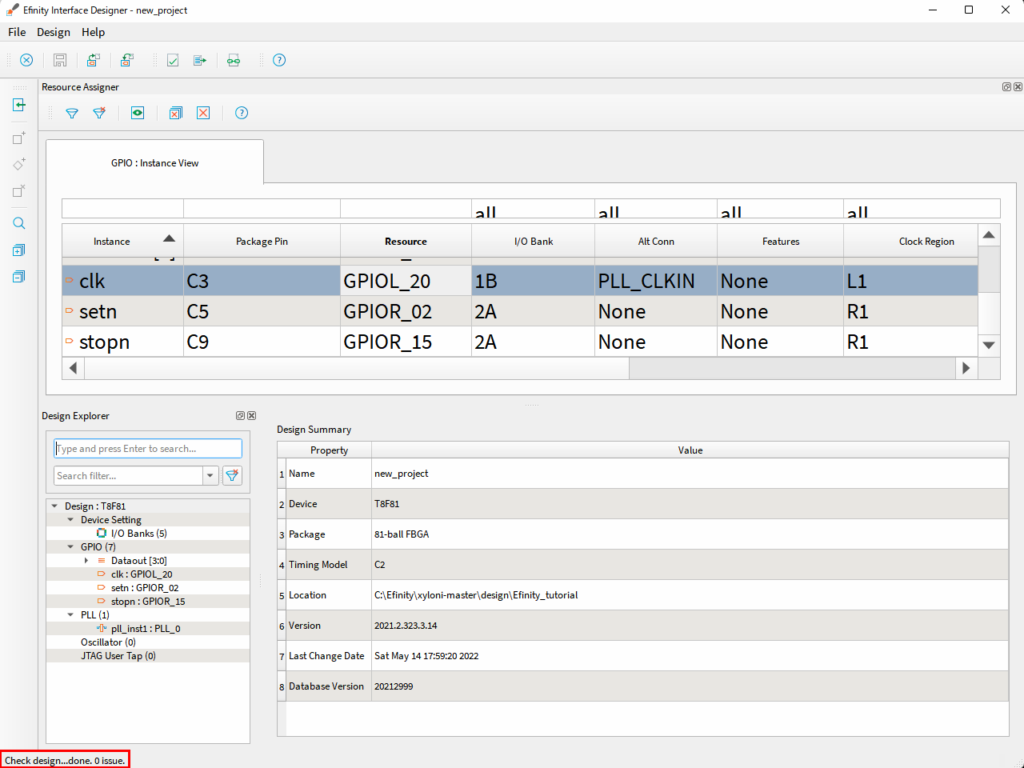

GPIO Resource AssignerでclkピンにGPIOL_20を割り当てます。

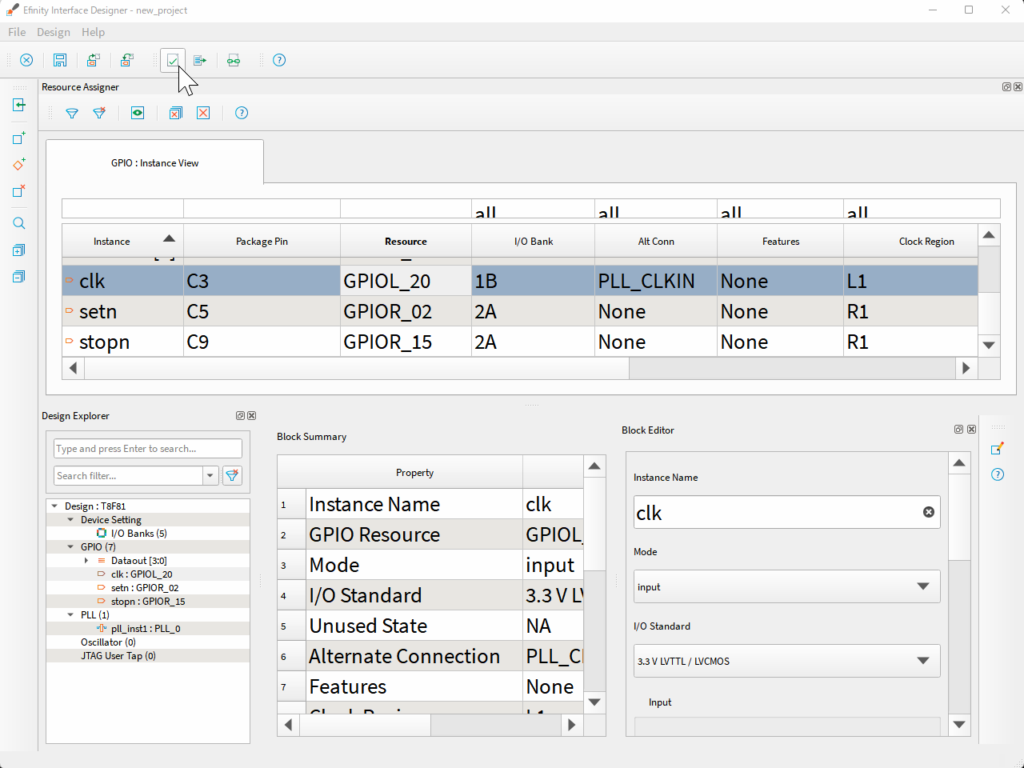

Check Designを行います。

間違えがなければ、Check design done. … 0 issue.とでます。

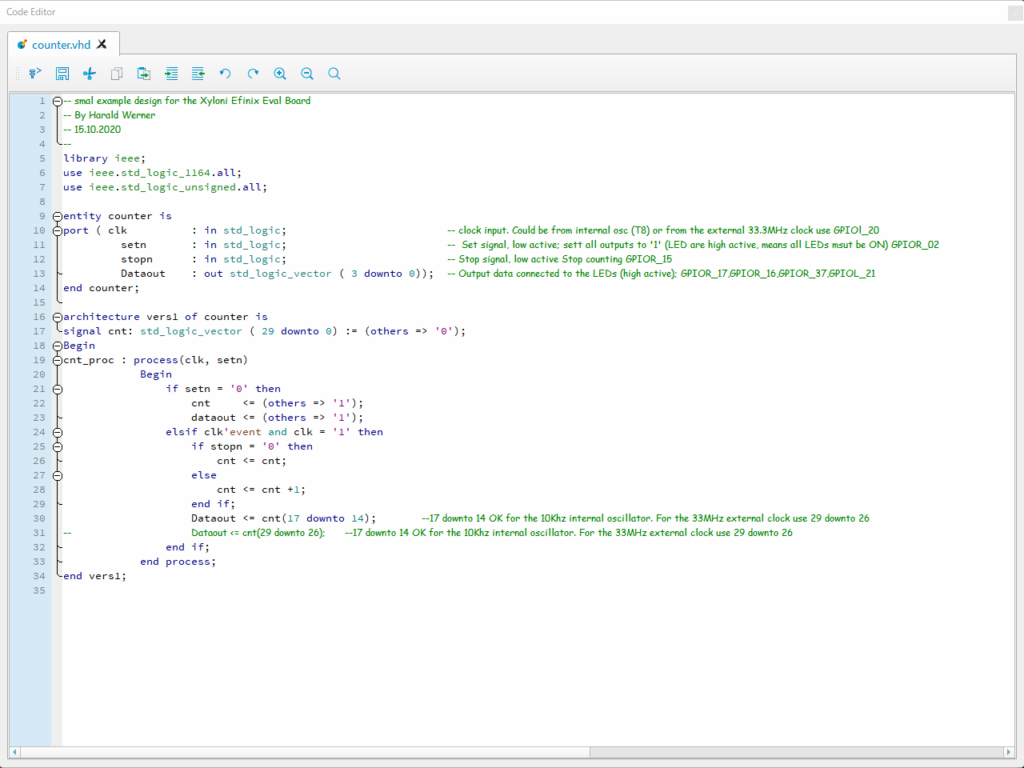

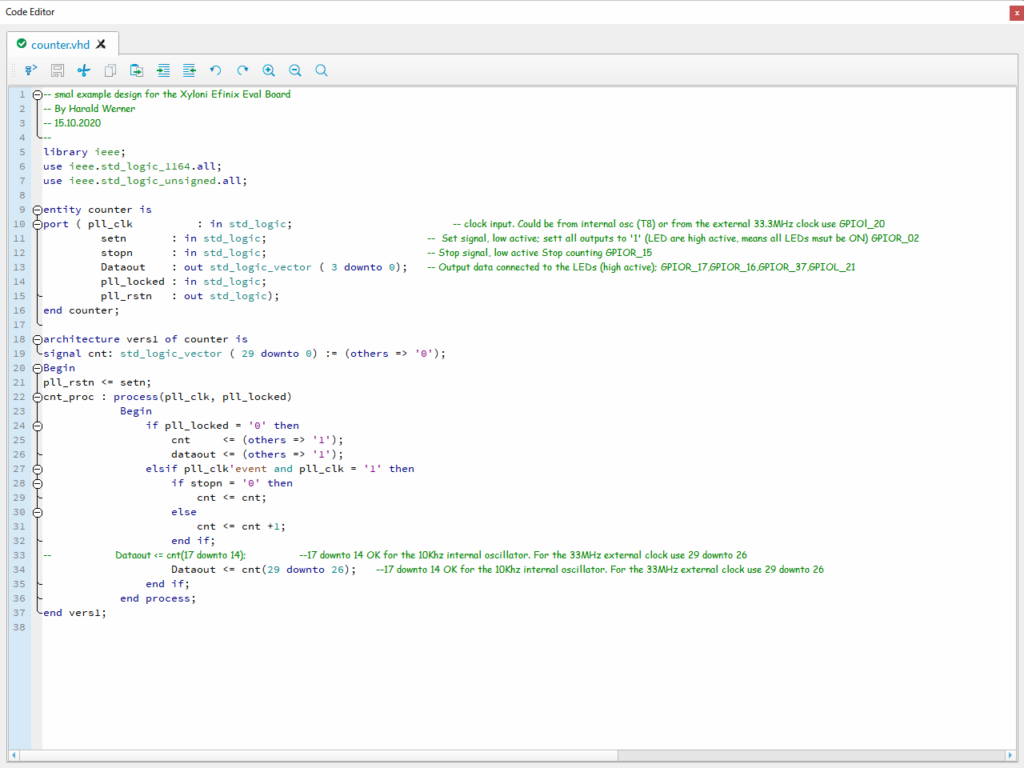

RTLの変更

- 入力ポート clkをpll_clkに変更

- 入力ポート pll_lockedと出力信号 pll_rstnを追加

- setnをpll_rstnに接続

- architecture文の中のclkをpll_clkに変更

- architecture文の中のsetnをpll_lockedに変更

- Dataout <= cnt(17 downto 14); から Dataout <= cnt(29 downto 26); に変更

-- smal example design for the Xyloni Efinix Eval Board

-- By Harald Werner

-- 15.10.2020

--

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity counter is

port ( pll_clk : in std_logic; -- clock input. Could be from internal osc (T8) or from the external 33.3MHz clock use GPIOl_20

setn : in std_logic; -- Set signal, low active; sett all outputs to '1' (LED are high active, means all LEDs msut be ON) GPIOR_02

stopn : in std_logic; -- Stop signal, low active Stop counting GPIOR_15

Dataout : out std_logic_vector ( 3 downto 0); -- Output data connected to the LEDs (high active); GPIOR_17,GPIOR_16,GPIOR_37,GPIOL_21

pll_locked : in std_logic;

pll_rstn : out std_logic);

end counter;

architecture vers1 of counter is

signal cnt: std_logic_vector ( 29 downto 0) := (others => '0');

Begin

pll_rstn <= setn;

cnt_proc : process(pll_clk, pll_locked)

Begin

if pll_locked = '0' then

cnt <= (others => '1');

dataout <= (others => '1');

elsif pll_clk'event and pll_clk = '1' then

if stopn = '0' then

cnt <= cnt;

else

cnt <= cnt +1;

end if;

-- Dataout <= cnt(17 downto 14); --17 downto 14 OK for the 10Khz internal oscillator. For the 33MHz external clock use 29 downto 26

Dataout <= cnt(29 downto 26); --17 downto 14 OK for the 10Khz internal oscillator. For the 33MHz external clock use 29 downto 26

end if;

end process;

end vers1;

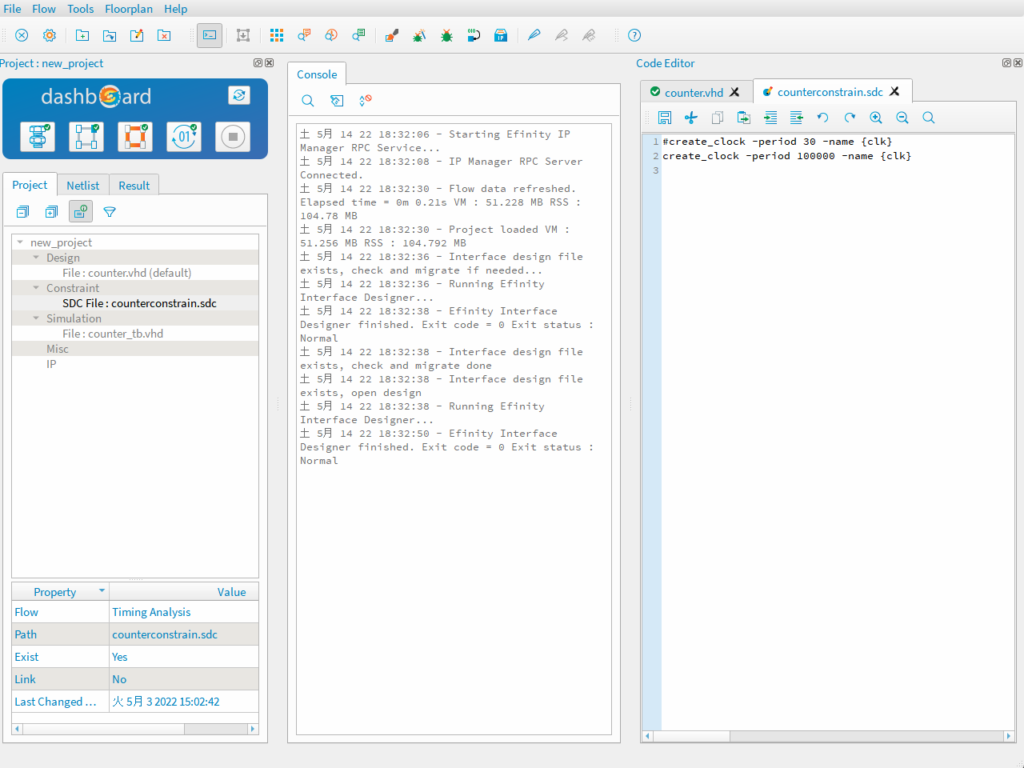

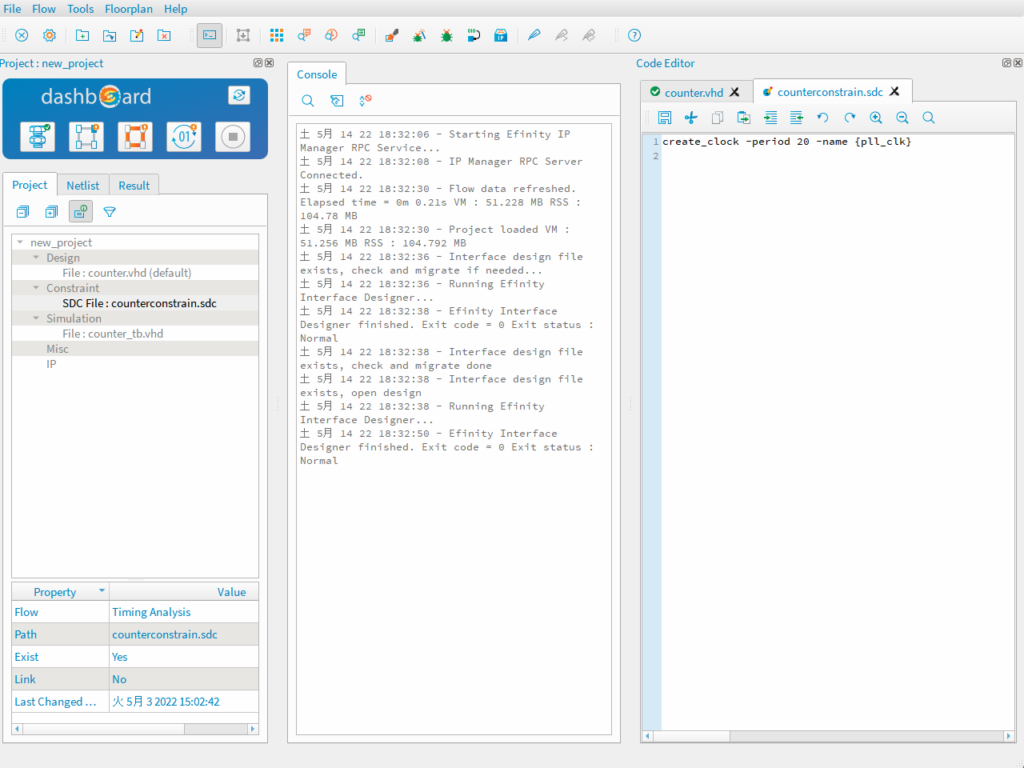

SDCファイルの変更

create_clock -periodを20 -nameを {pll_clk}に変更します。

合成と書き込み

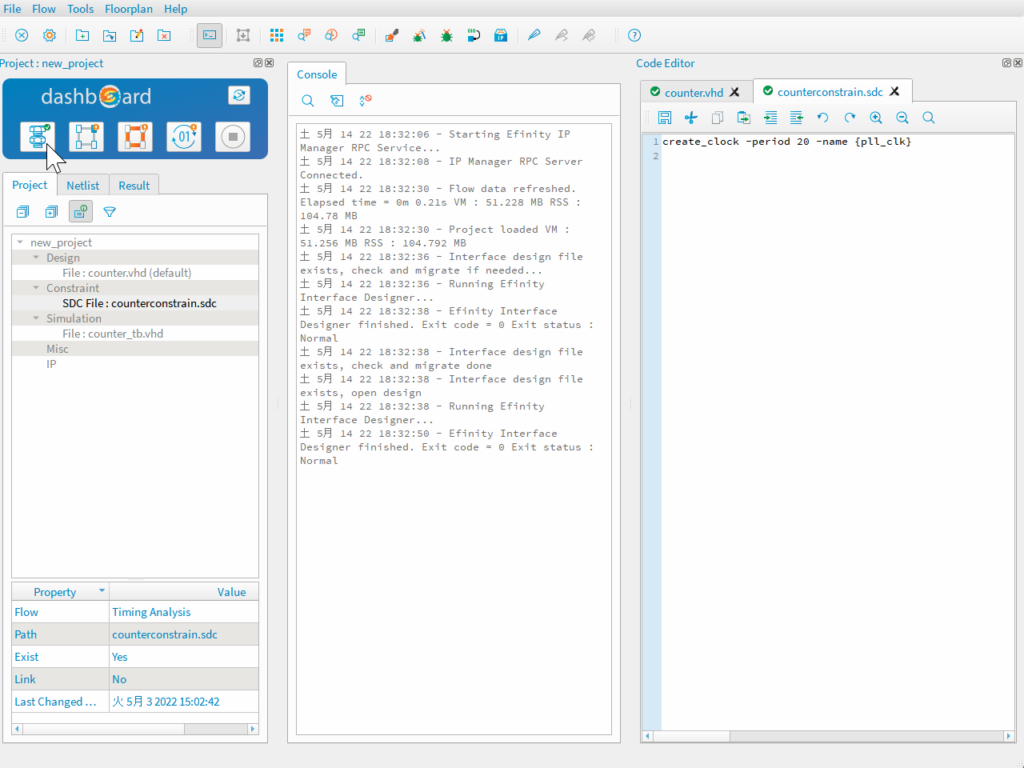

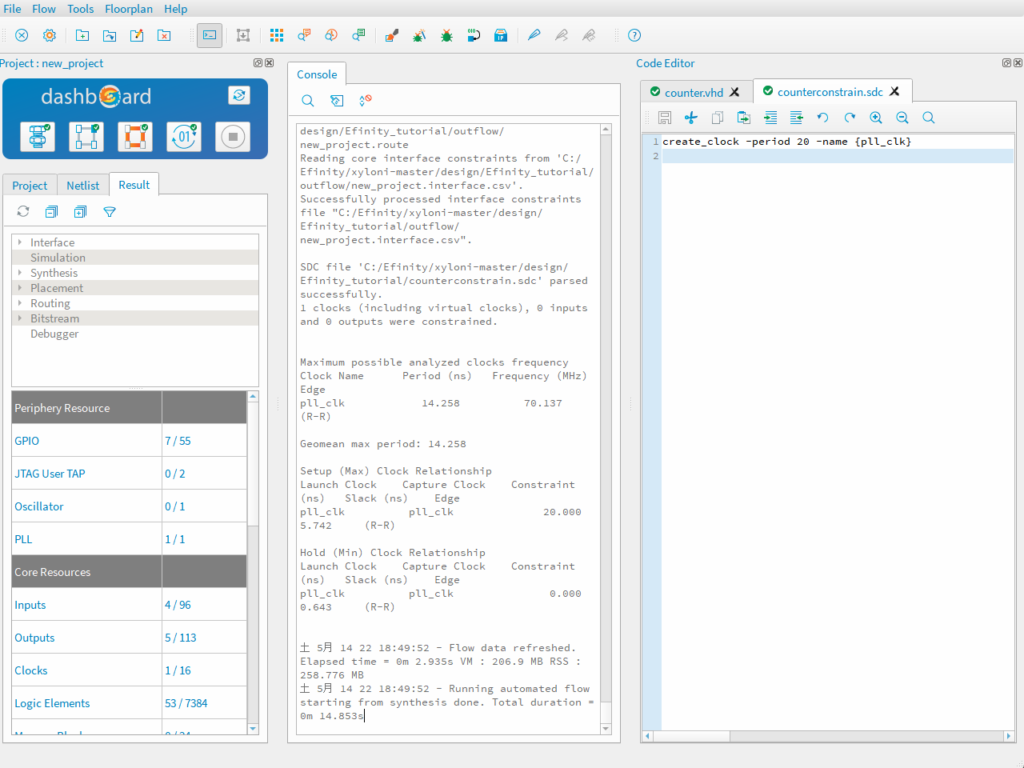

合成します。

合成は成功しました。Maximum clockも70MHzと問題ありません。

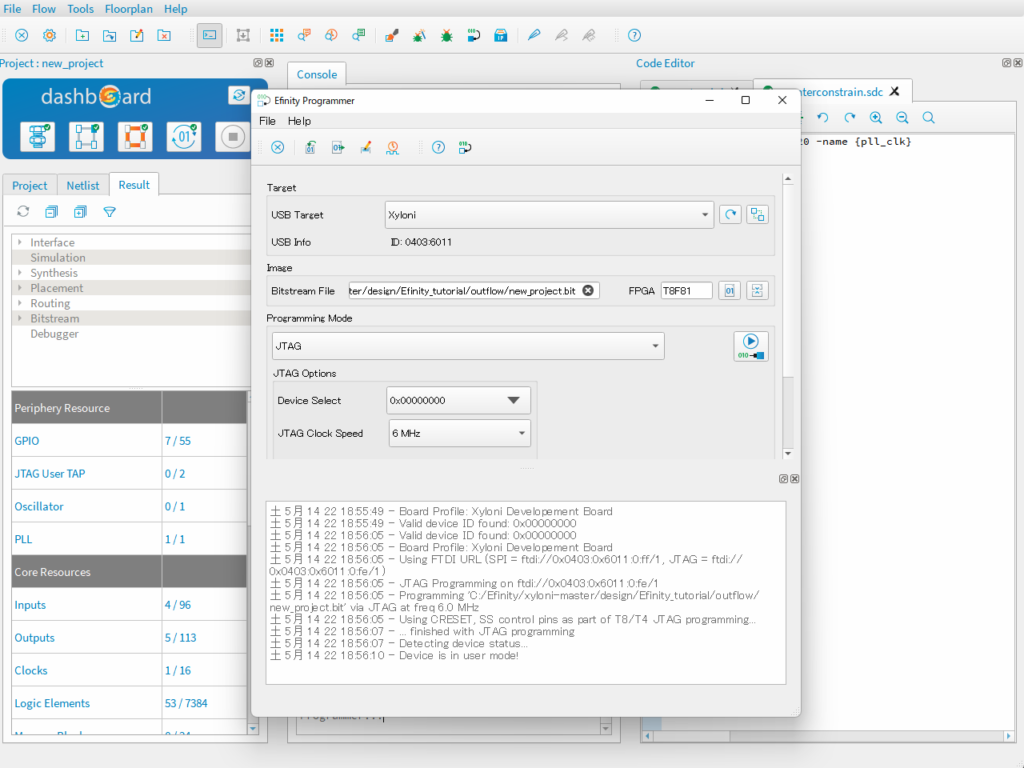

では、FPGAに書き込んでみます。

動作確認

チュートリアルのときと比較してLEDの周期が早くなりました。(わかりにくいですが、【Xyloni®開発キット チュートリアルでStudy】の動画と比較してみてください)

回路構成のイメージ

最後に回路構成のイメージを図示してみました。

最後に、関連記事Efinix Trion デバイス毎のPLLの仕様の相違点についてもご一読いただけますと幸いです。