EFINIX Trion True Dual-Port Memoryでは、Read Enableは実装できない

作成者:mou-mou

DPRAMのVerilog-HDLでの記述については、Efinity® Synthesis User Guideの「RAM」チャプターに記載されています。Simple Dual-Port Memory(1 port read / 1 port write) と True Dual-Port Memory(2 port read / 2 port write)の例があがっております。Simple Dual-Port Memoryにはrd_en信号を使用した例があるのに対して、True Dual-Port Memoryにはrd_en信号を使用した例がありません。

そこで、実際に True Dual-Port Memory Examples にRead Enable信号を記述してみました。

module ram512x8_tdp_mix (wdataA, addrA, clkA, weA, rdataA, wdataB, addrB, clkB, weB, reB, rdataB);

parameter AWIDTH = 9;

parameter DWIDTH = 8;

localparam DEPTH = 1 << AWIDTH;

localparam MAX_DATA = (1<<DWIDTH)-1;

input [DWIDTH-1:0] wdataA, wdataB;

input [AWIDTH-1:0] addrA, addrB;

input clkA, weA;

input clkB, weB;

input reB;

output reg [DWIDTH-1:0] rdataA, rdataB;

reg [DWIDTH-1:0] mem [DEPTH-1:0];

integer i;

initial begin

// The memory is initialized with

// decreasing values startingfrom MAX_DATA

for (i=0;i<DEPTH;i=i+1)

mem[i] = MAX_DATA - i;

end

always@(posedge clkA) begin

// Use blocking assignments to for read-first

rdataA = mem[addrA];

if (weA) begin

mem[addrA] = wdataA;

end

end

always@(posedge clkB) begin

// Use blocking assignments to force write-first

if (weB) begin

mem[addrB] = wdataB;

end

// rdataB = mem[addrB];

if (reB) begin // Read Enable

rdataB = mem[addrB];

end

end

endmoduleすると、以下のエラーが発生しました。

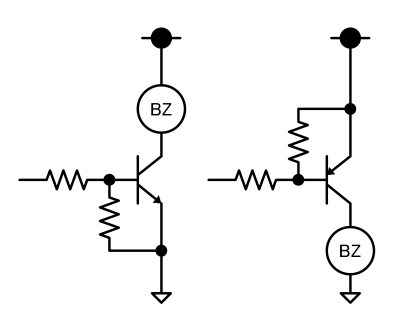

[EFX-0680 ERROR] Dual Ported Memory 'mem' has incompatible Read-Enable signal 'reB'. (C:/Efinity\ram512x8_tdp_mix\ram512x8_tdp_mix.v:13)Quantum Trion® Primitives User Guide の EFX_RAM_5K と EFX_DPRAM_5Kを見比べると、EFX_RAM_5Kには[RE]ポートが存在しますが、EFX_DPRAM_5Kには[RE]ポートは存在しません。

Simple Dual-Port MemoryにはEFX_RAM_5Kが割り当てらるためRead Enableを実装できるが、True Dual-Port MemoryにはEFX_DPRAM_5Kが割り当てられるためRead Enableは実装できないということになります。