EFINIX Efinty iVerilog シミュレーション

作成者:mou-mou

ここでは、FINIX Efintyのドキュメント内で記載されているシミュレータのうち無償で使用することができる iVerilog(Icarus Verilog)を使用したシミュレーションについて紹介いたします。

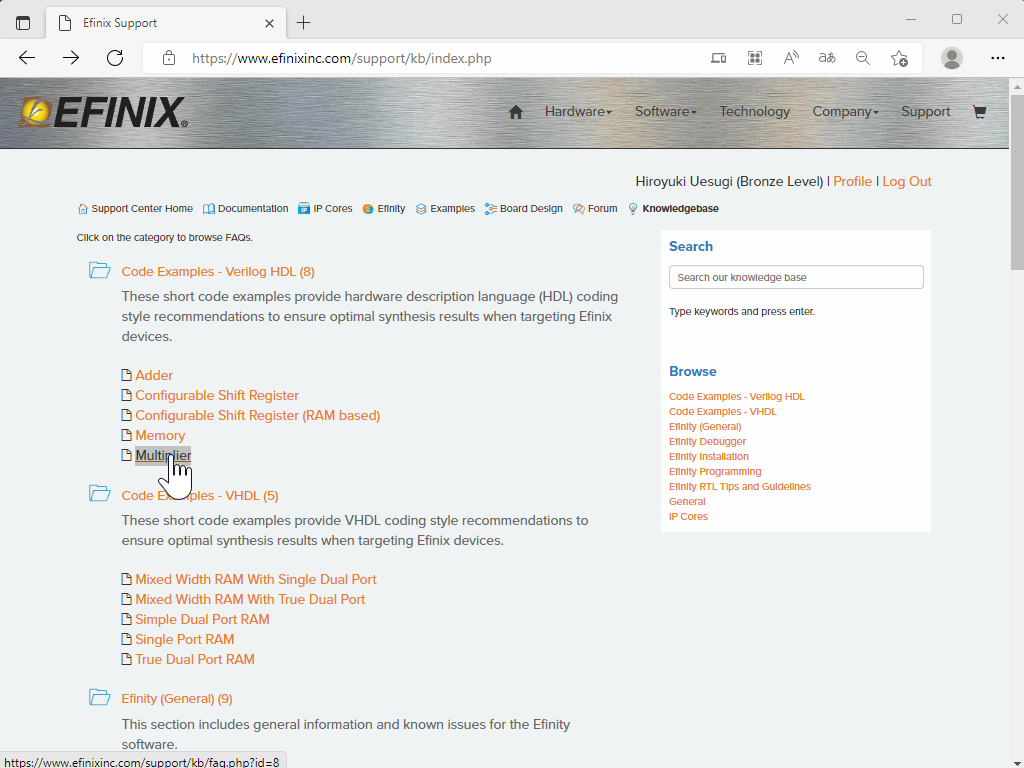

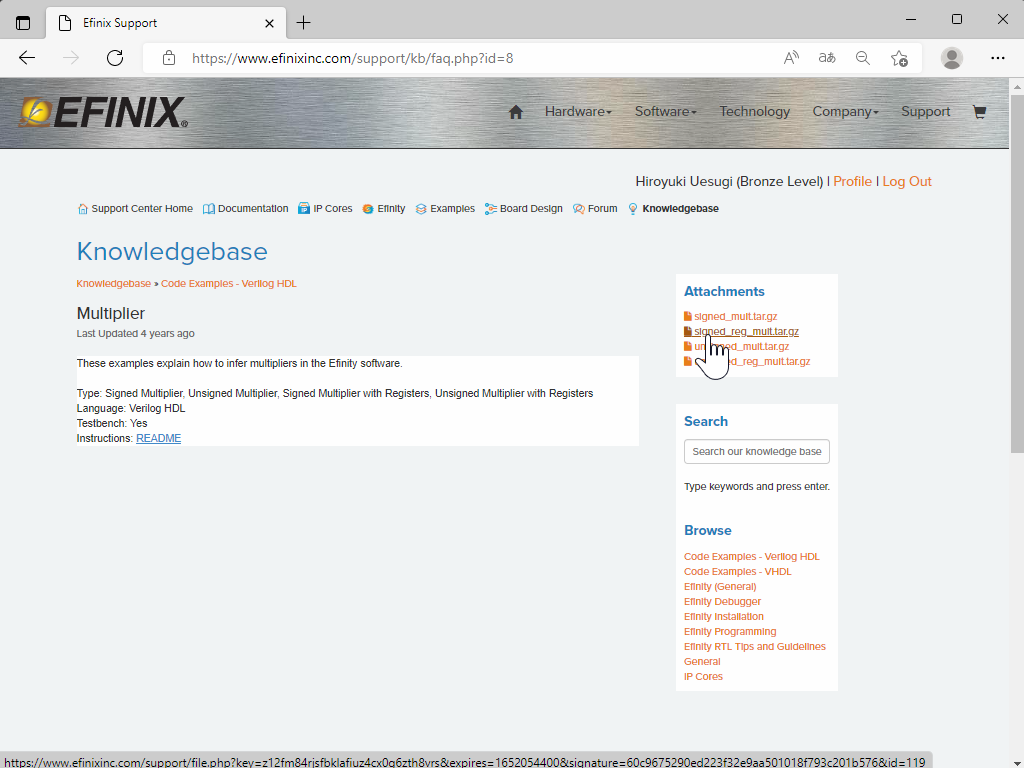

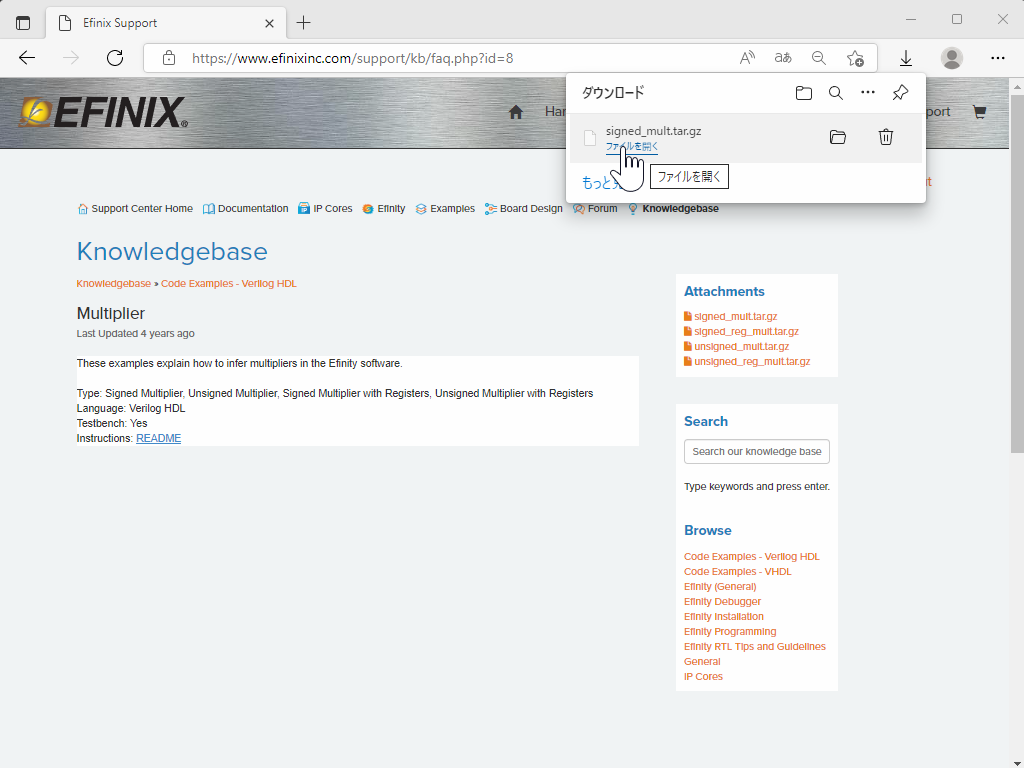

Knowledgebase にある Code Examples – Verilog HDL の中から Multiplier の signed_reg_mult.tar.gz を使用してシミュレーションをしていきます。

の手順で進めていきます。

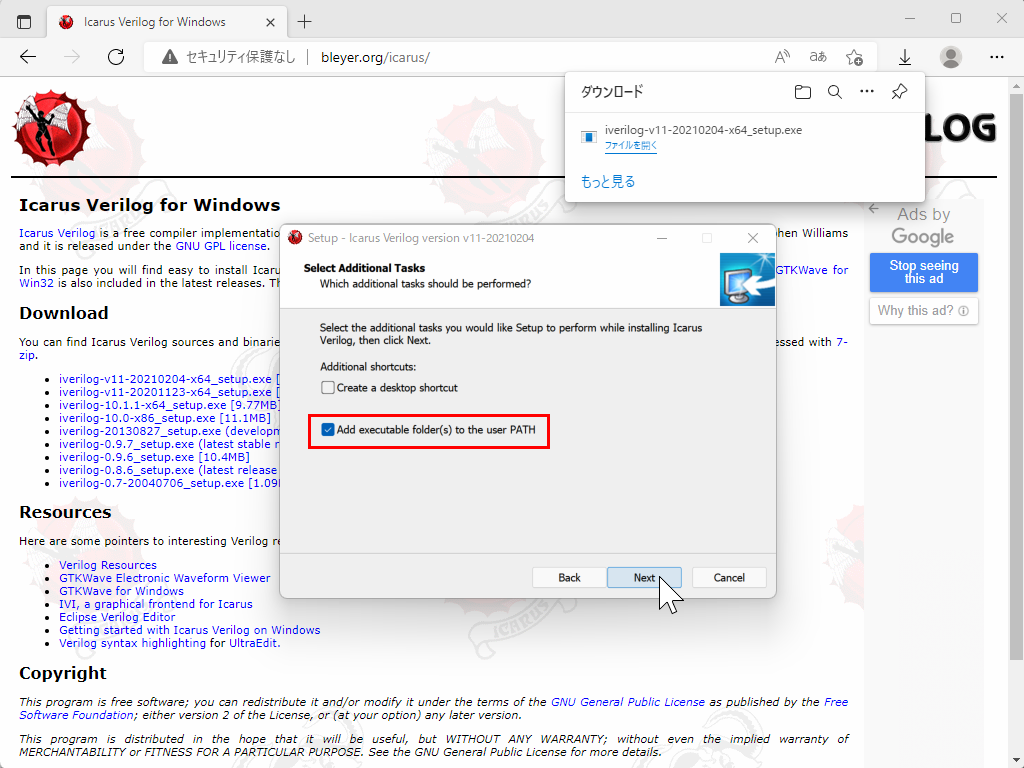

iVerilog(Icarus Verilog)のインストール

Icarus Verilog for Windows から iverilog-v11-20210204-x64_setup.exe [44.1MB]をダウンロードしてきます。

基本的にはディフォルトのままインストールを進めますが、user PATHが通るようにチェックボックスをチェックしてください。

Efinity での signed_reg_mult プロジェクト作成

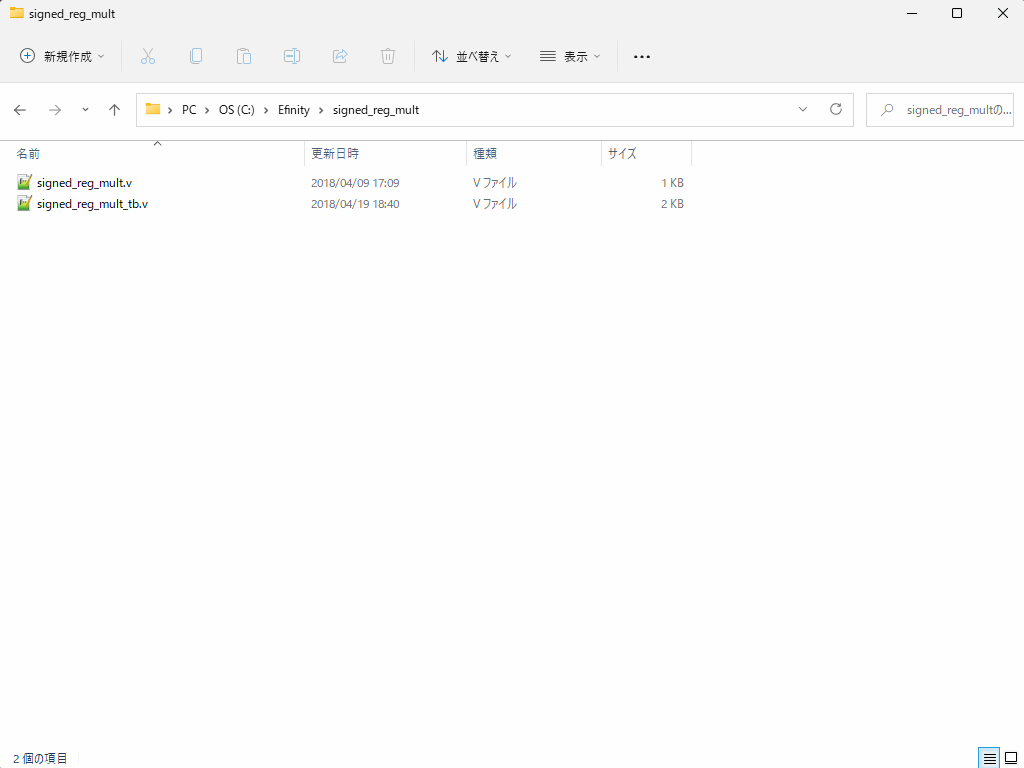

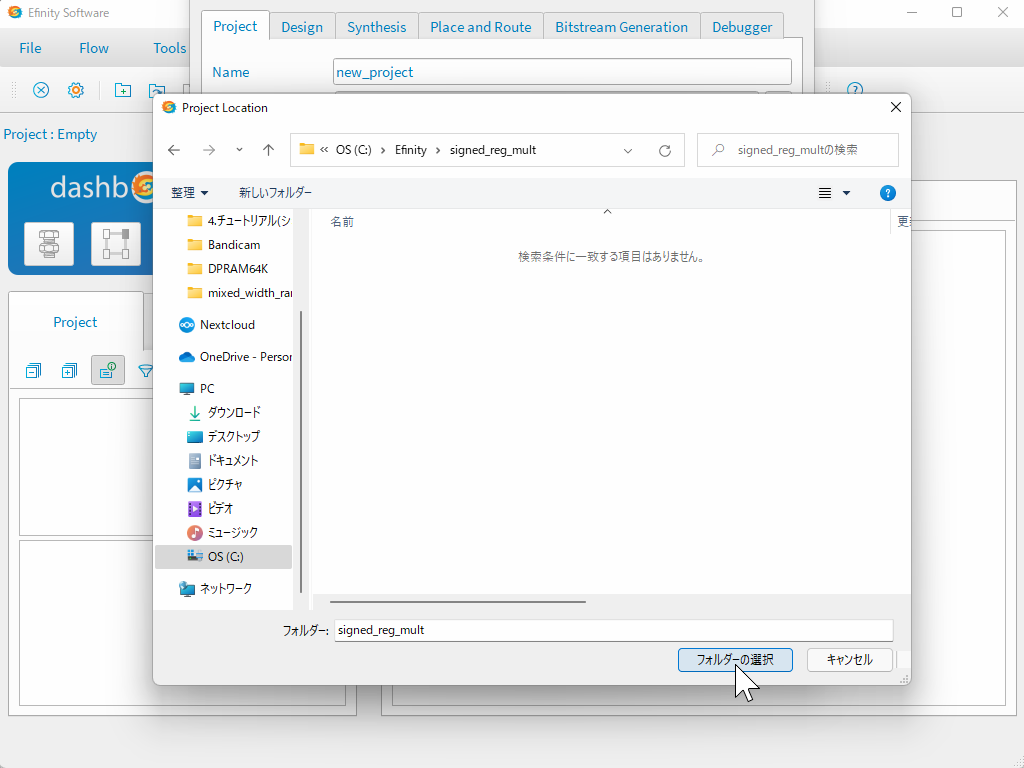

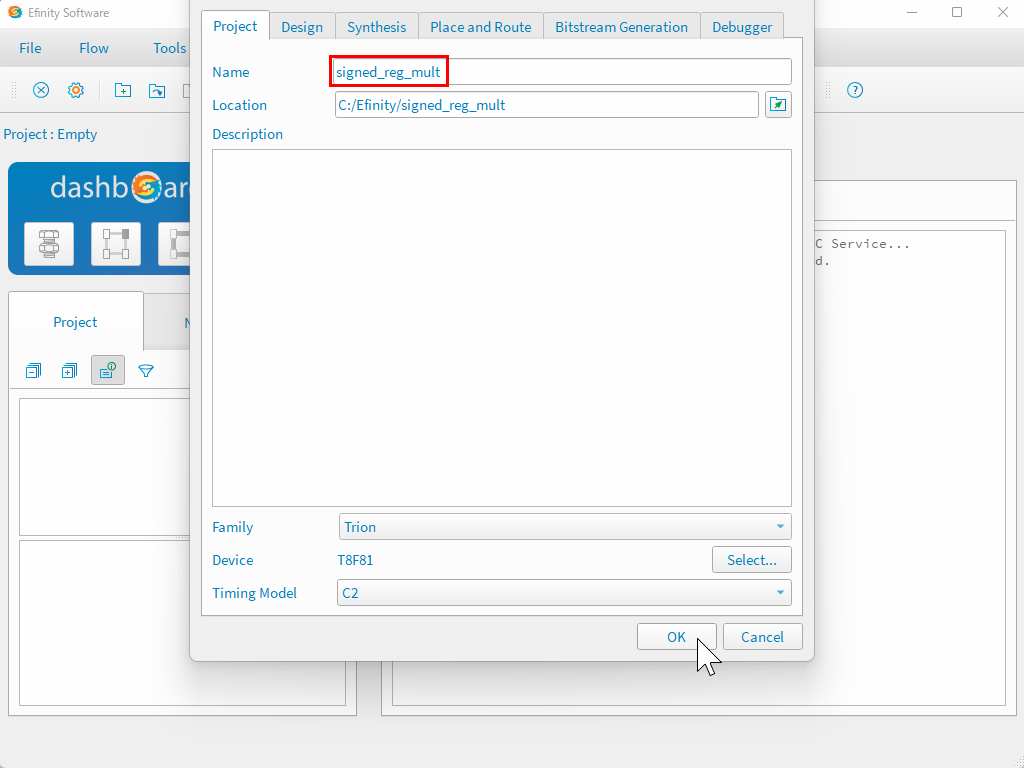

nowledgebaseのMultiplierからsigned_reg_mult.tar.gz をダウンロードし任意のフォルダに解凍します。ここでは、C:\Efinityに解凍して進めていきます。

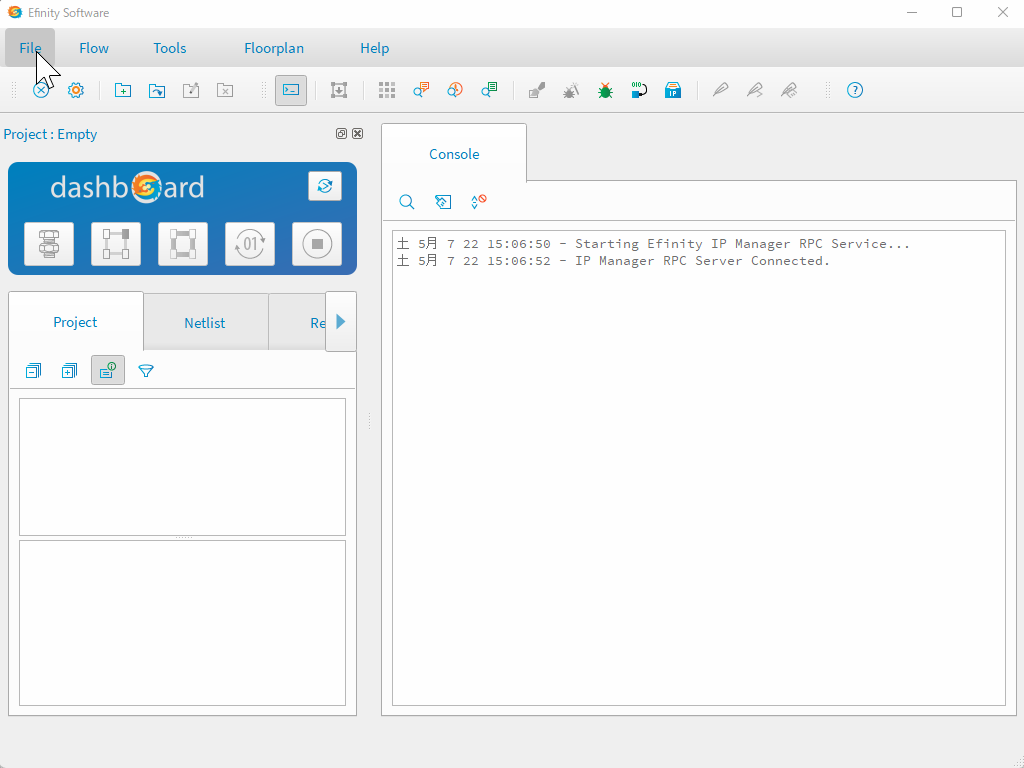

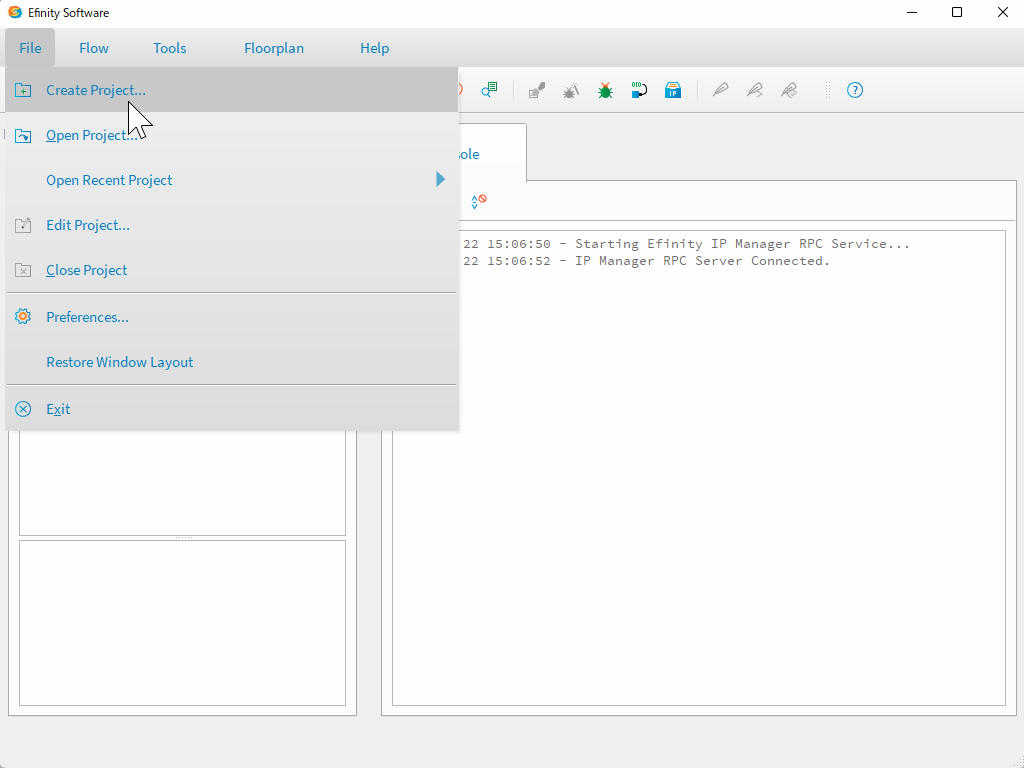

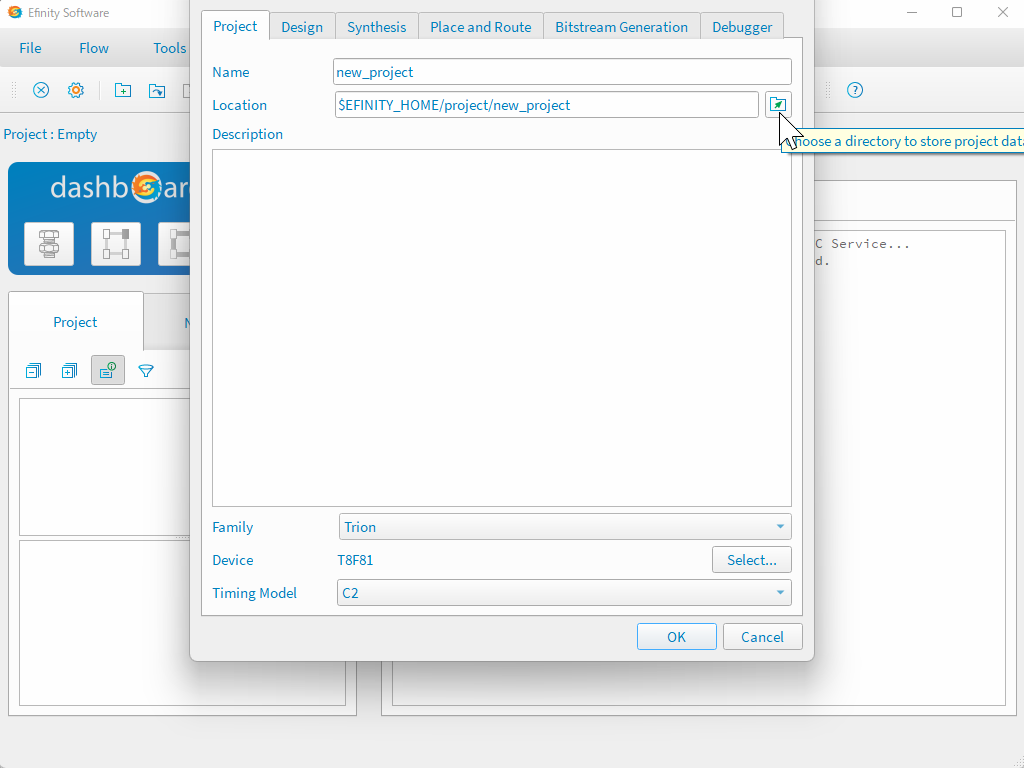

Efinityを起動してプロジェクトを作成します。

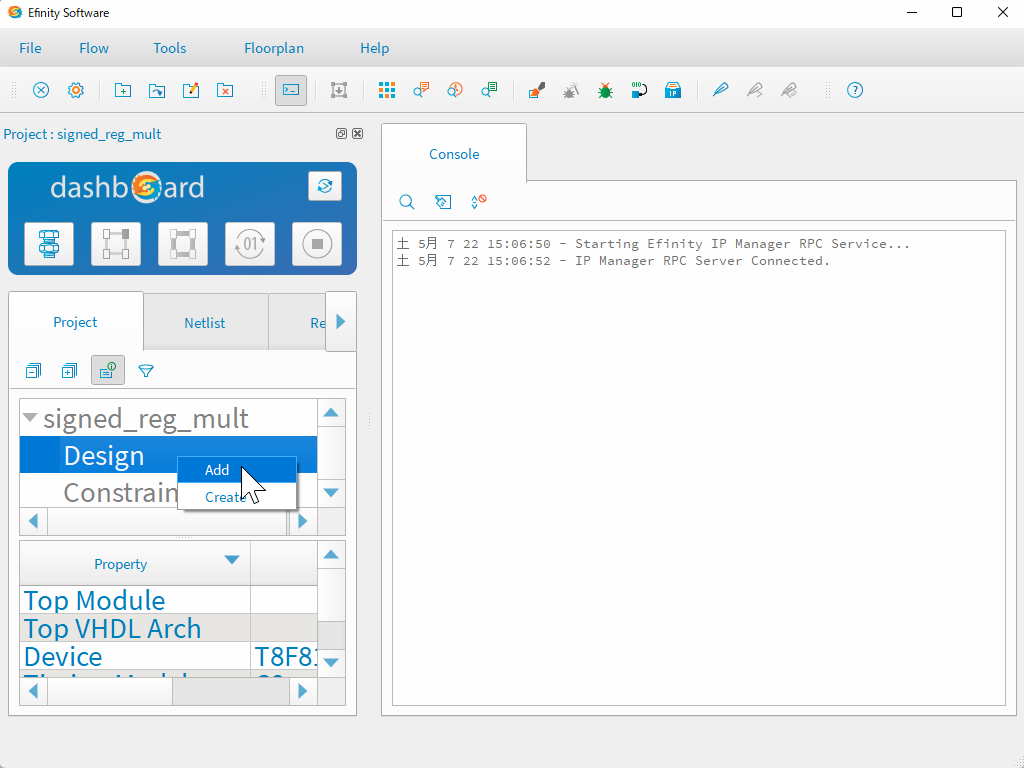

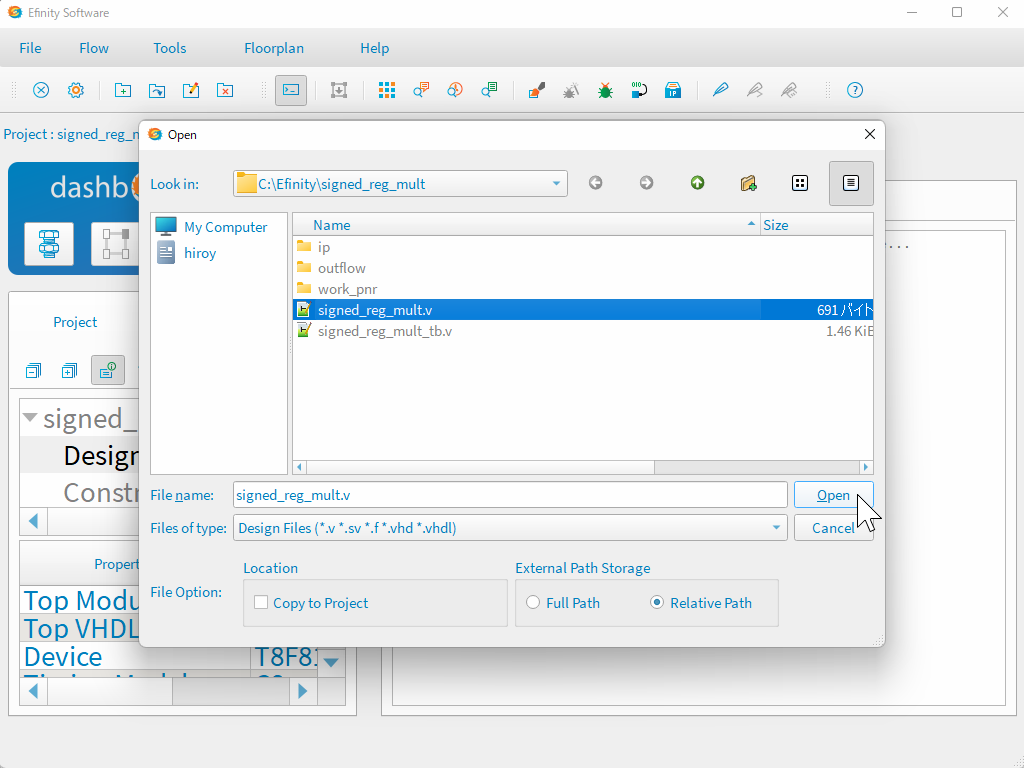

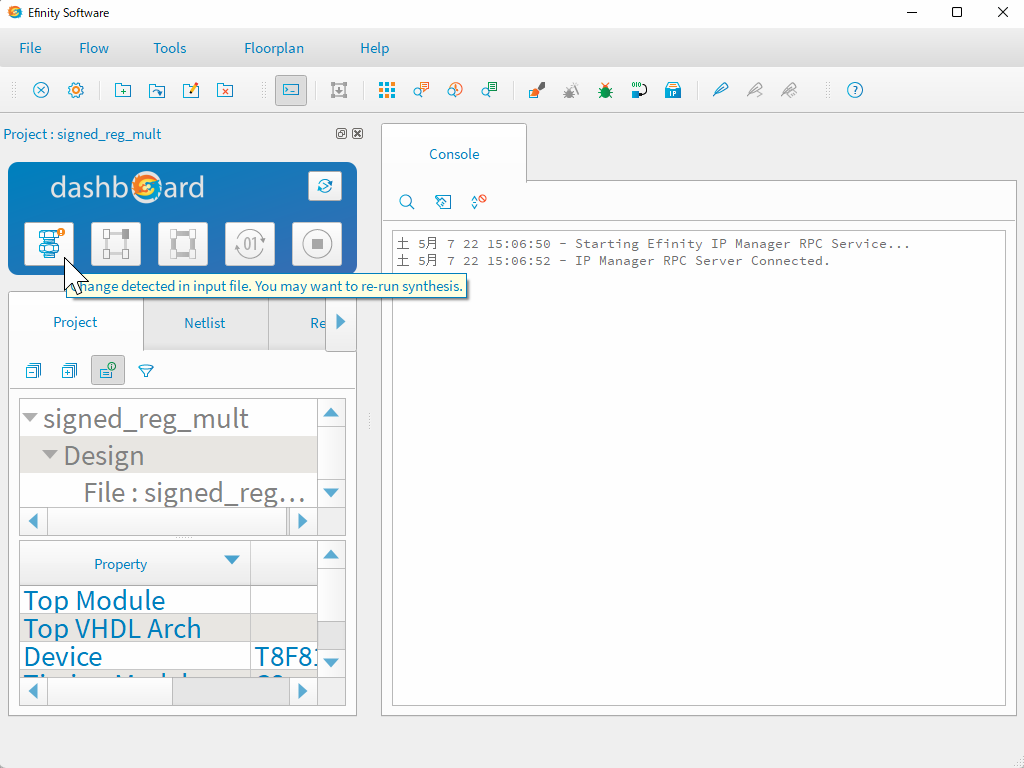

signed_reg_multをプロジェクトに追加します。

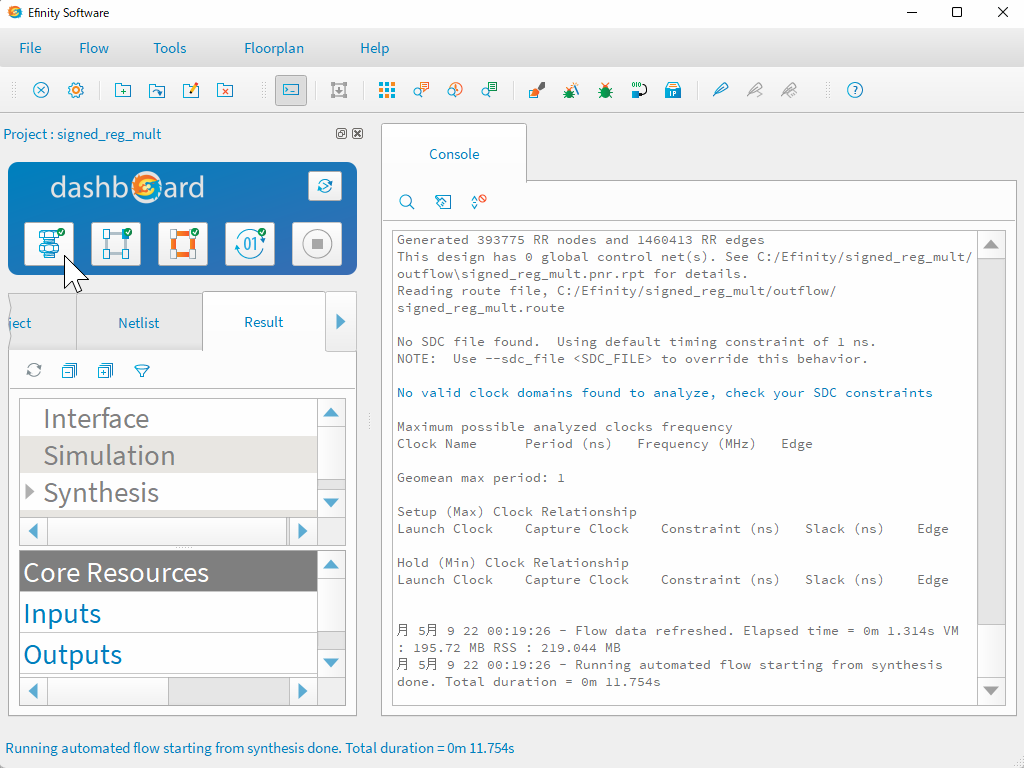

合成します。

シミュレーションの実行

iVerilog(Icarus Verilog)をつかってシミュレーションを実行します。

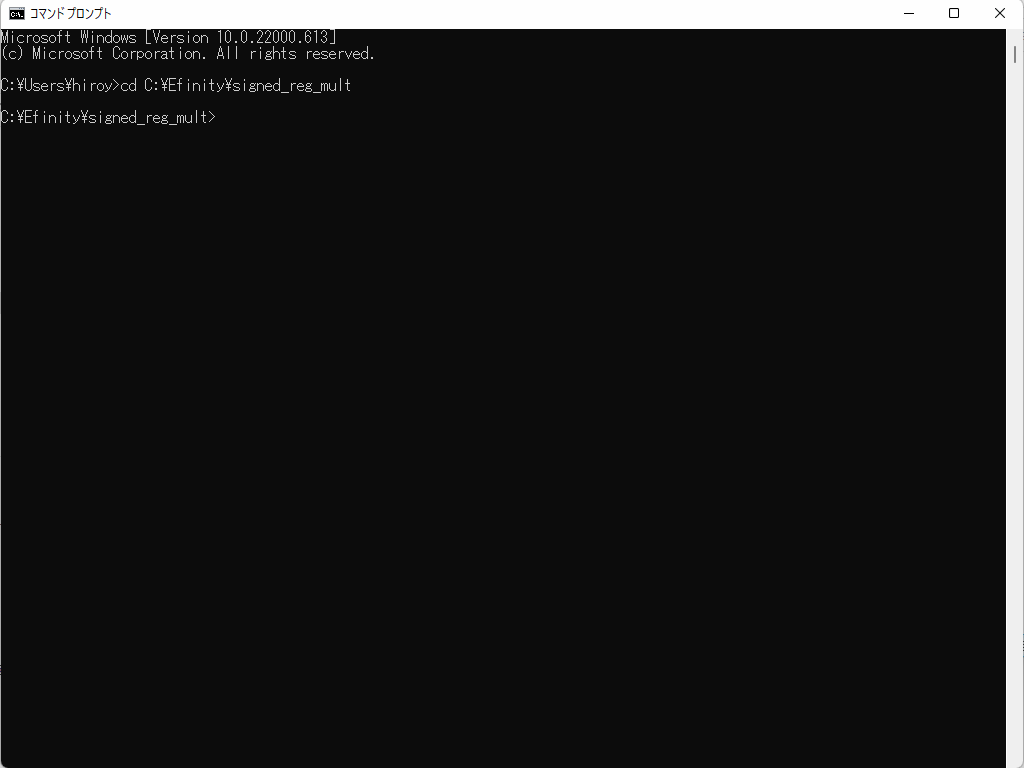

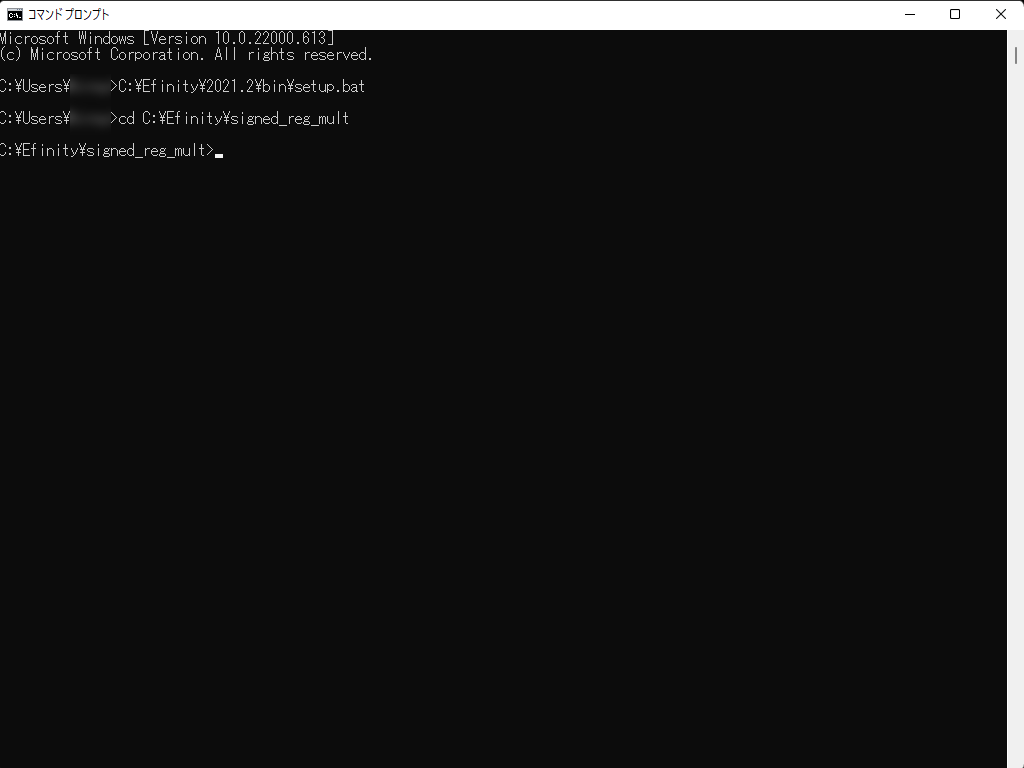

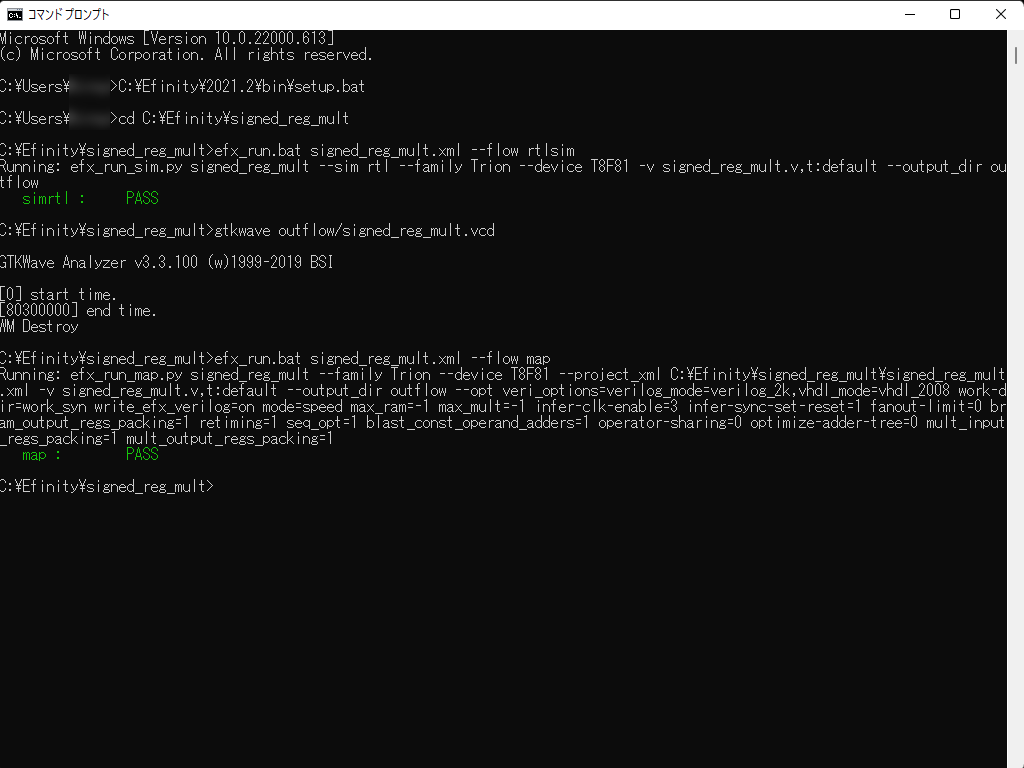

コマンドプロンプトを起動して、C:\Efinity\2021.2\bin\setup.batを実行します。このバッチファイルを実行することで必要なパスの設定や環境変数の設定が行われます。

プロジェクトのフォルダに行きます。

Behavioral(RTL)シミュレーション

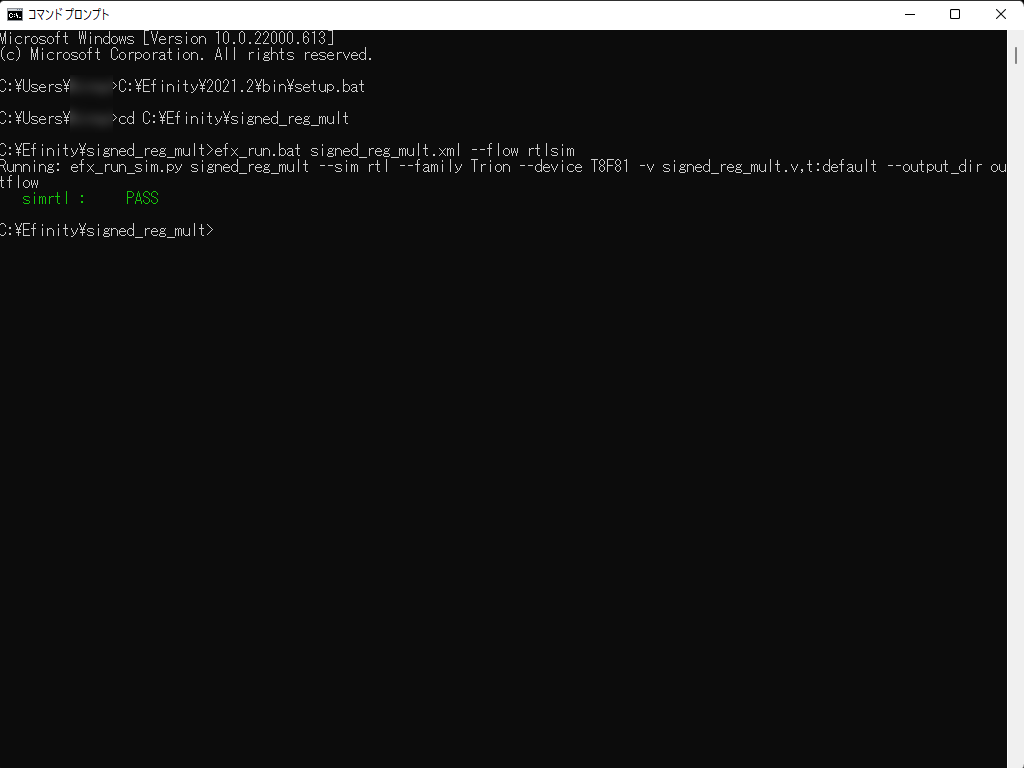

efx_run.bat signed_reg_mult.xml –flow rtlsim と入力して Behavioral(RTL)シミュレーションを実行します。

simrtl : PASSと出力されると成功です。outflowフォルダにsigned_reg_mult.rtl.simlogが出力されます。記述のエラーがある等でPASSが出力されない場合は、logファイルを確認します。

efx_run.batの引数で –tb はテストベンチファイルを指します。 プロジェクト名(xmlのファイル名)の末尾に_tbを付加した場合は、省略できます。–tb_topは、テストベンチのトップモジュール名を指定します。トップモジュール名が[sim]であれば省略できます。

省略しない場合は、以下のようになります。

efx_run.bat signed_reg_mult.xml –flow rtlsim –tb signed_reg_mult_tb.v –tb_top sim

テストベンチファイル signed_reg_mult_tb.v の中を見てみます。

$dumpfile("outflow/signed_reg_mult.vcd");

$dumpvars(0, sim);$dumpfileによって、outflowフォルダにsigned_reg_mult.vcdというシミュレーション結果のダンプファイルが出力されます。$dumpvarsでダンプを取る対象として、テストベンチのトップモジュールを指定します。

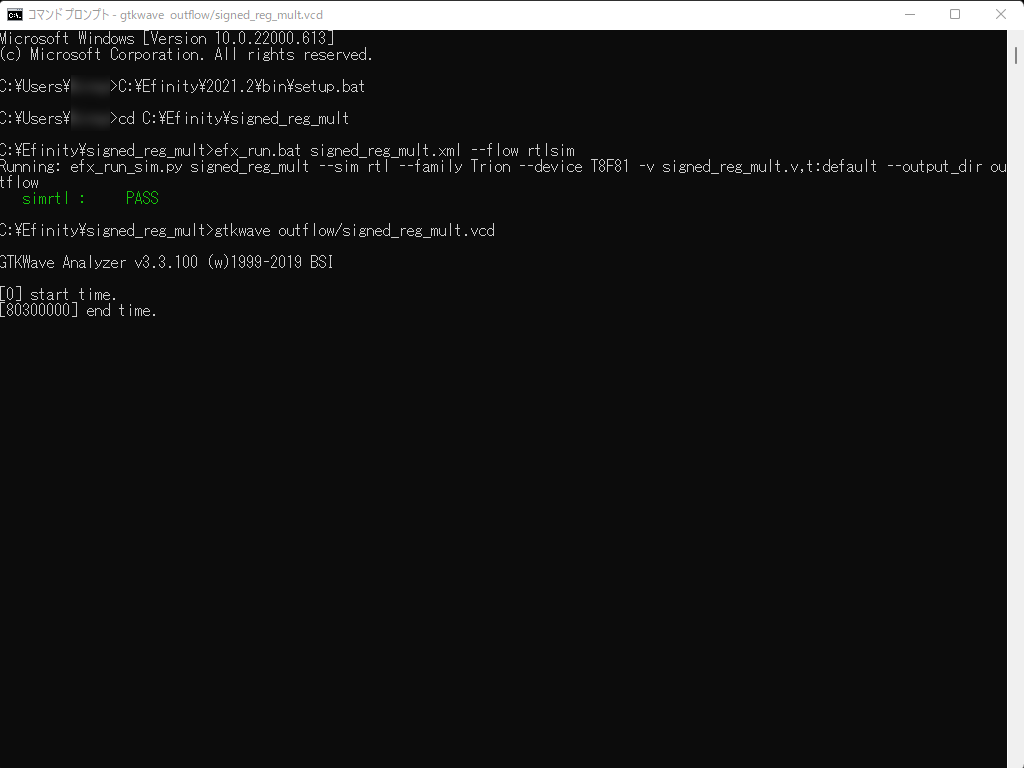

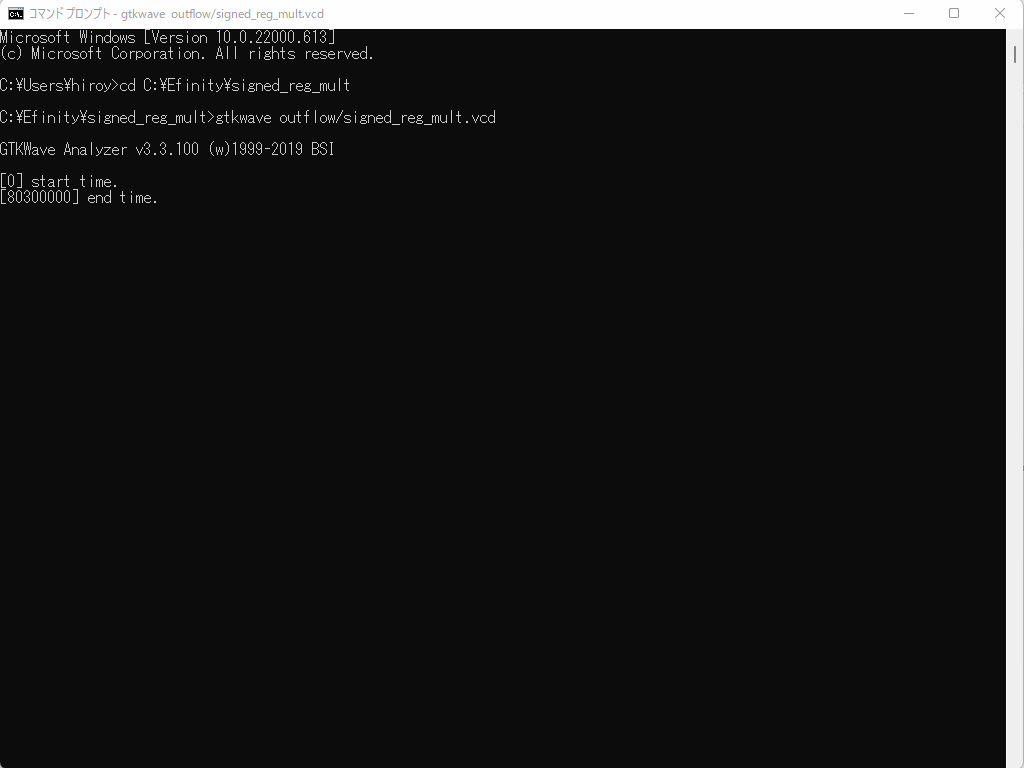

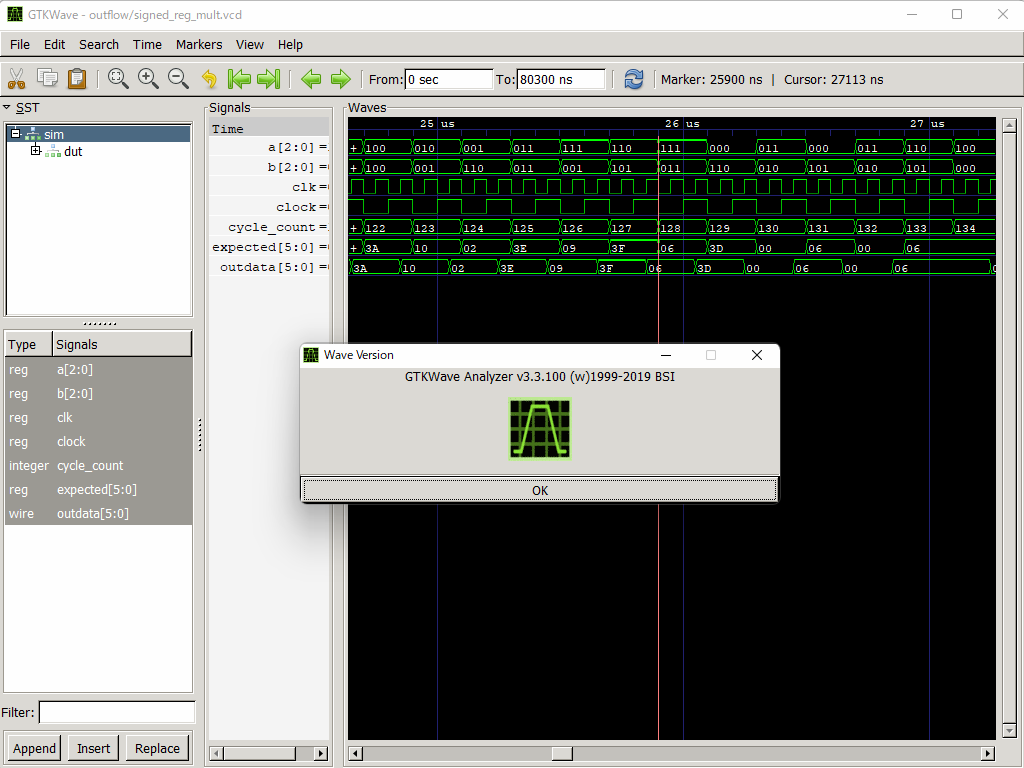

波形を表示します。gtkwave outflow/signed_reg_mult.vcdと入力します。

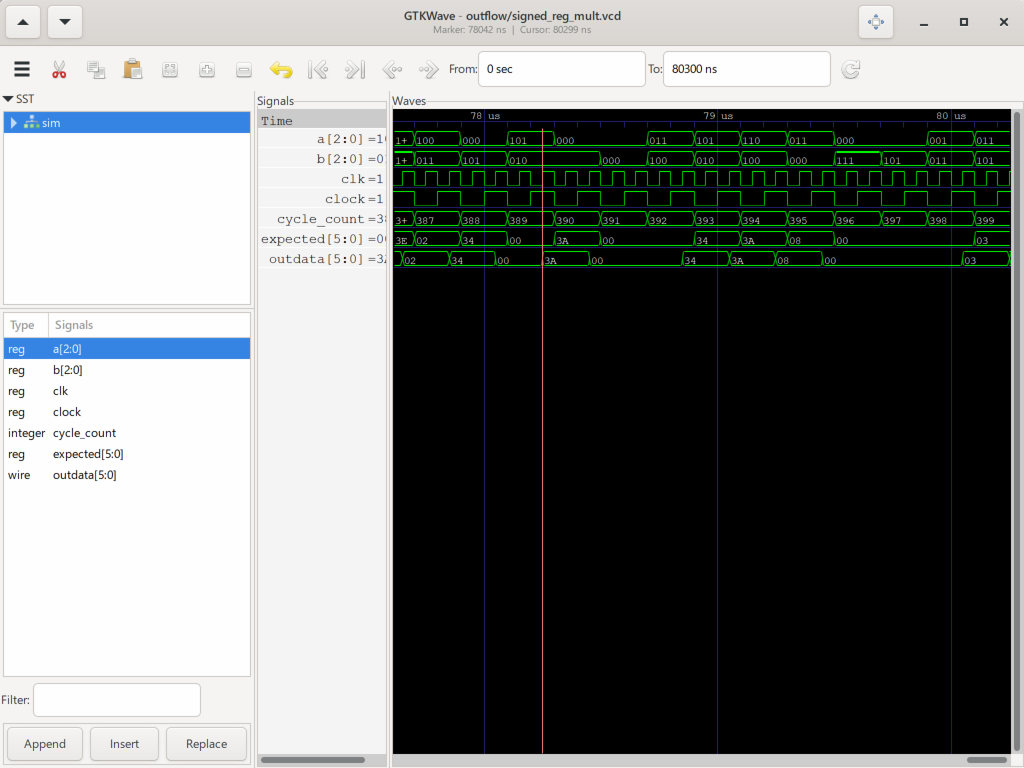

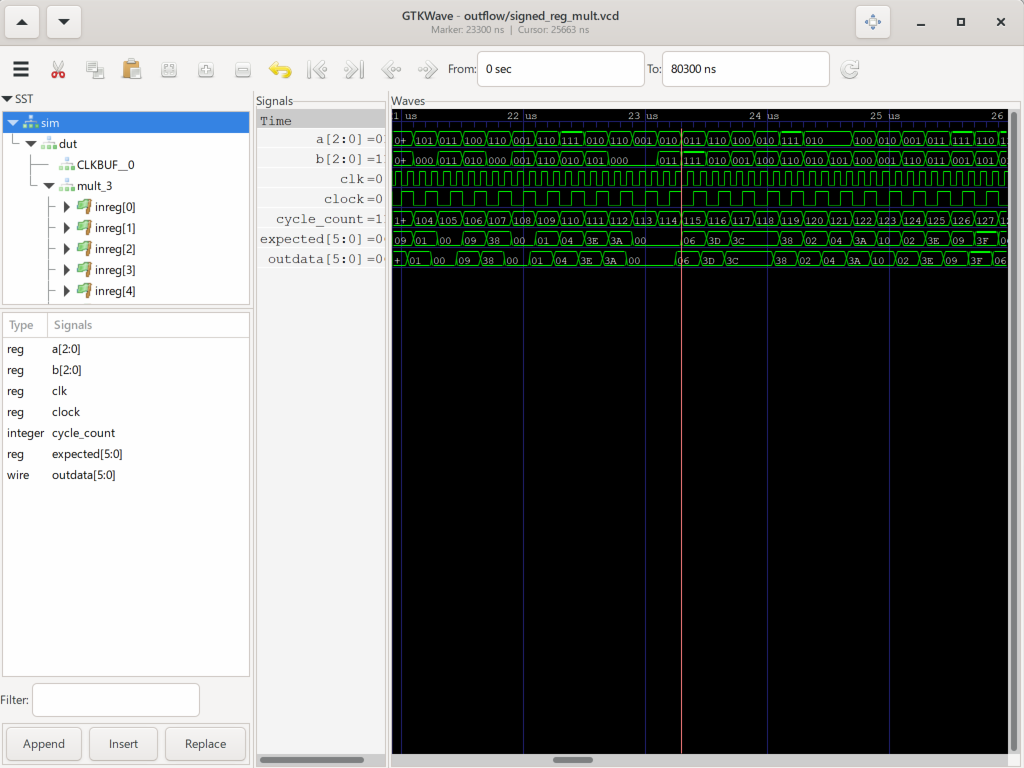

GTKWaveが立ち上がりますので、信号を選択して波形の確認を行います。

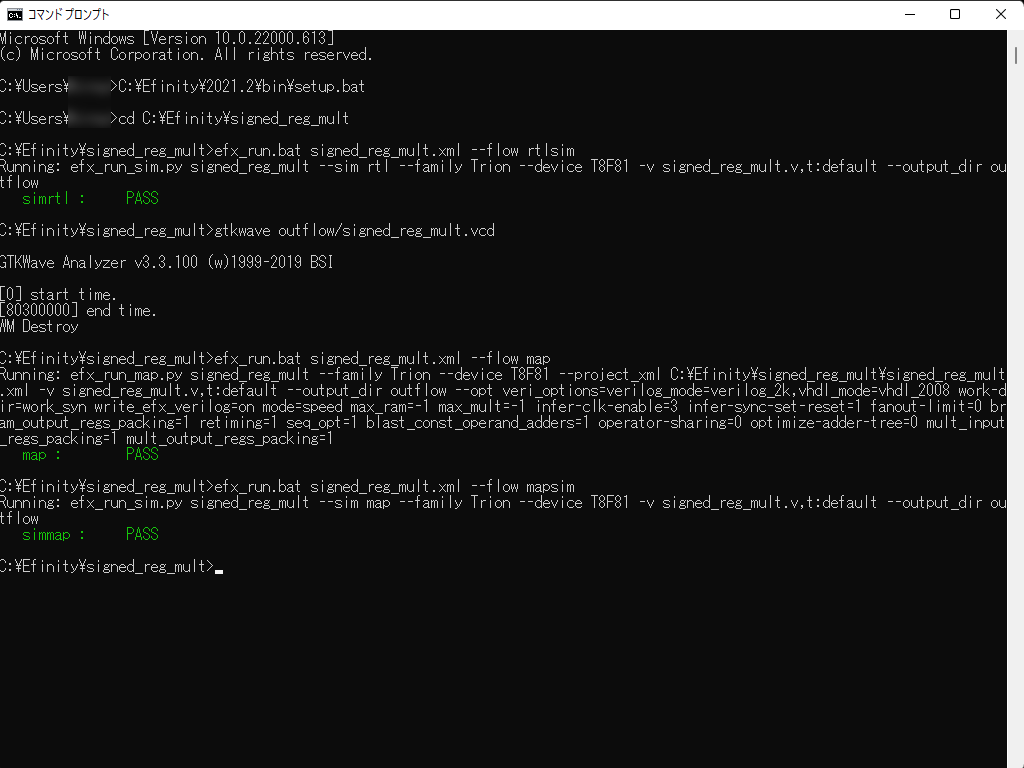

Post-synthesis(Post-MAP) シミュレーション

まずは、合成を実行します。efx_run.bat signed_reg_mult.xml –flow mapと入力します。

map : PASSと出力されると成功です。これでoutflowフォルダの下にsigned_reg_mult.map.vが出力されます。signed_reg_mult.logにログが出力されます。記述のエラーがある等でPASSが出力されない場合は、signed_reg_mult.err.logファイルを確認します。

Post-synthesis(Post-MAP) シミュレーションを実行します。efx_run.bat signed_reg_mult.xml –flow mapsimと入力します。ここでも、–tb -tb_topの引数は省略します。

imrtl : PASSと出力されると成功です。outflowフォルダにsigned_reg_mult.map.simlogが出力されます。

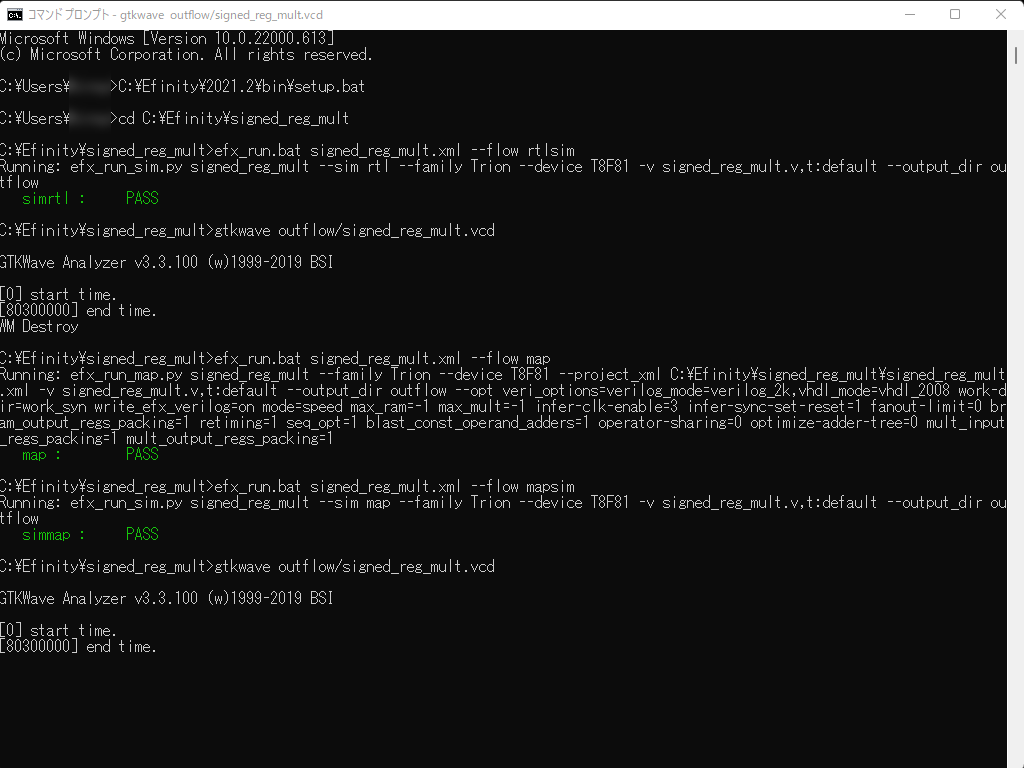

波形を表示します。gtkwave outflow/signed_reg_mult.vcdと入力します。

GTKWaveが立ち上がりますので、信号を選択して波形の確認を行います。

ツリーを開いていくと、CLKBUFやmult_3が見えます。RTLでなくPost-synthesisのシミュレーションになっていることがわかります。

GTKWaveの別バージョンへの差し替え

最後にiVerilog for Windowsをインストールするとセットでインストールされる波形ビュアーGTKWaveの挙動がいまいちよくないので、違うバージョンに差し替える手順を紹介いたします。

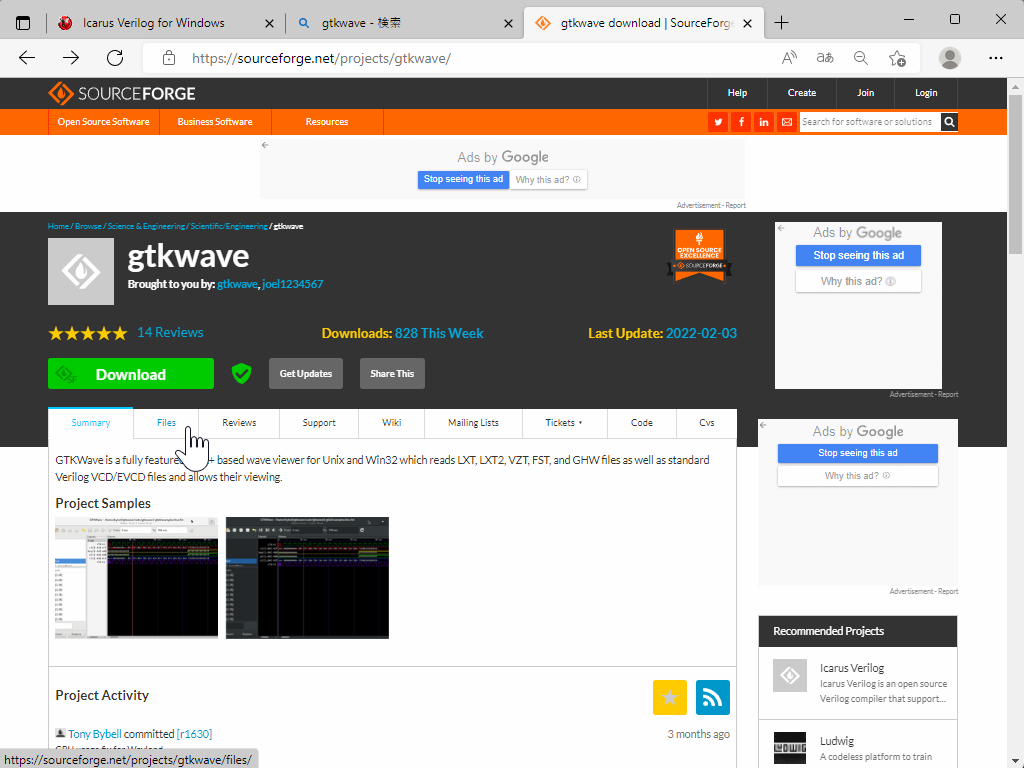

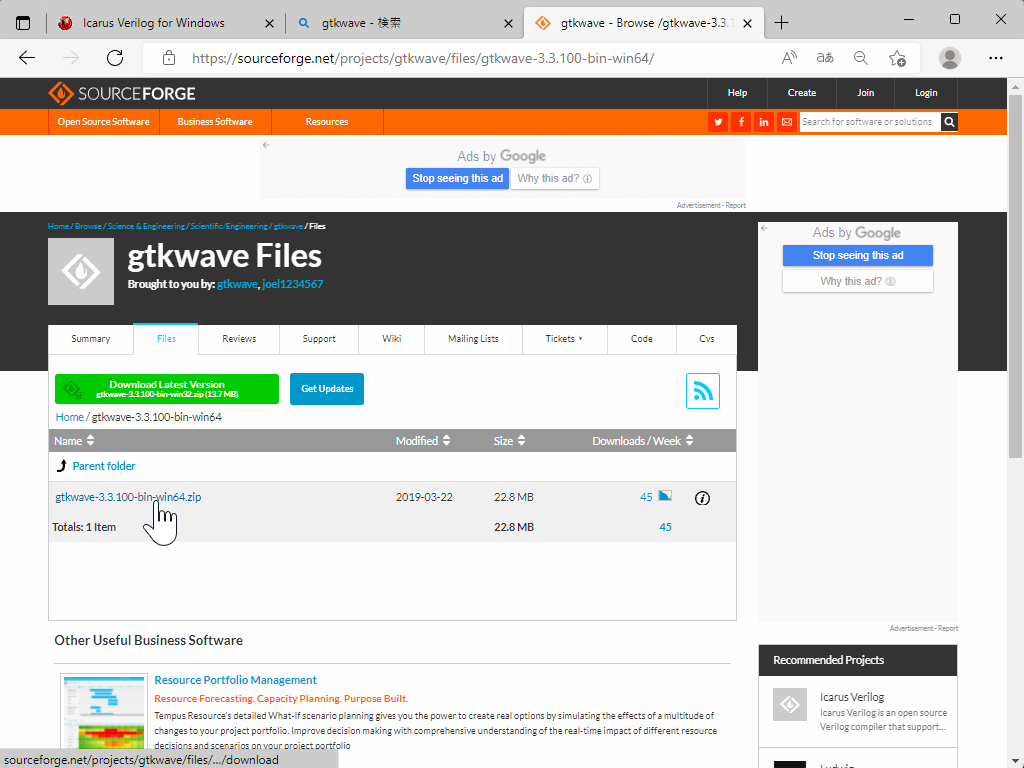

gtkwaveはSOURCEFORGEに公開されております。

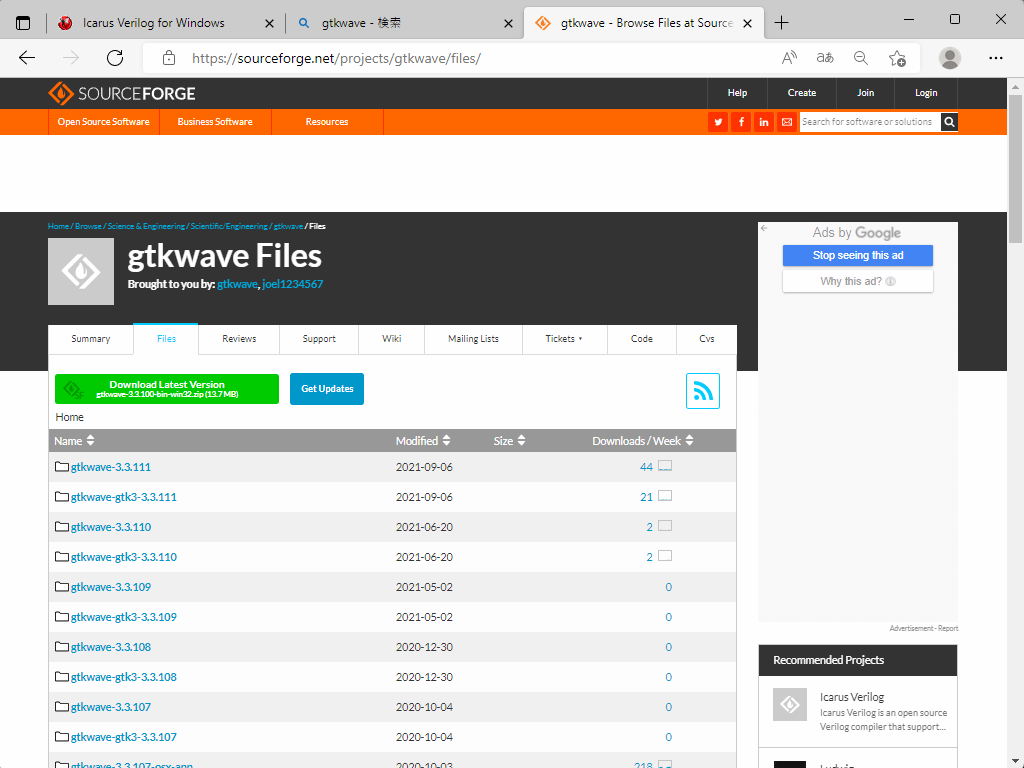

アップロードされているファイルをみてみます。

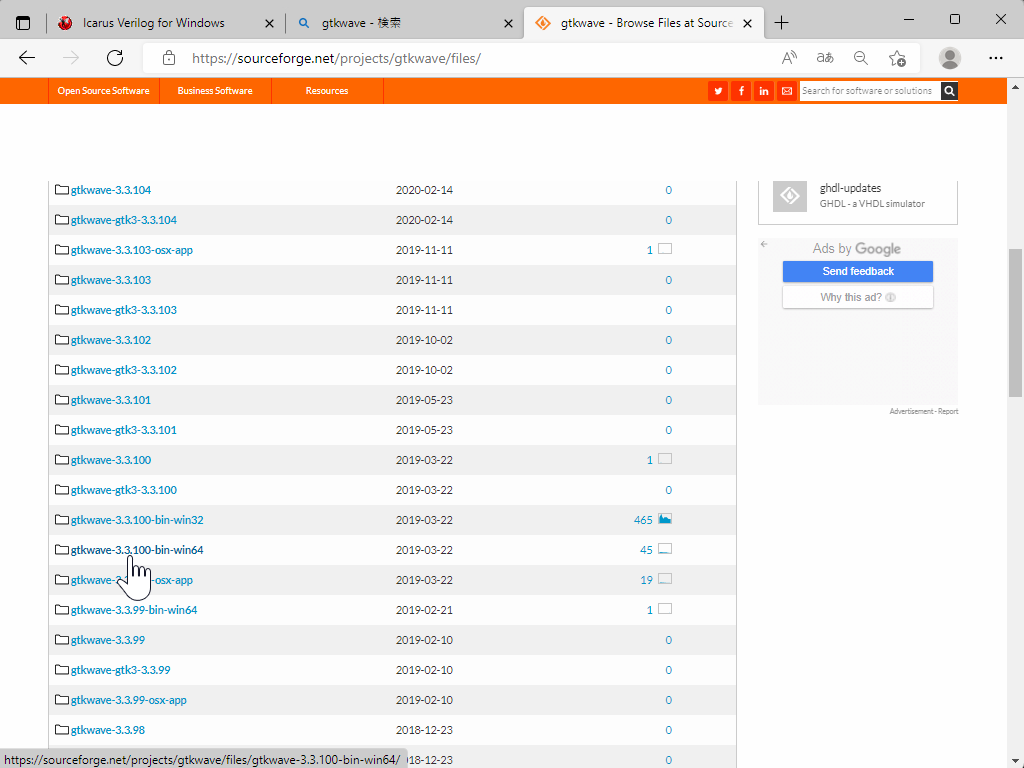

Win64の最新の3.3.100を選択します。

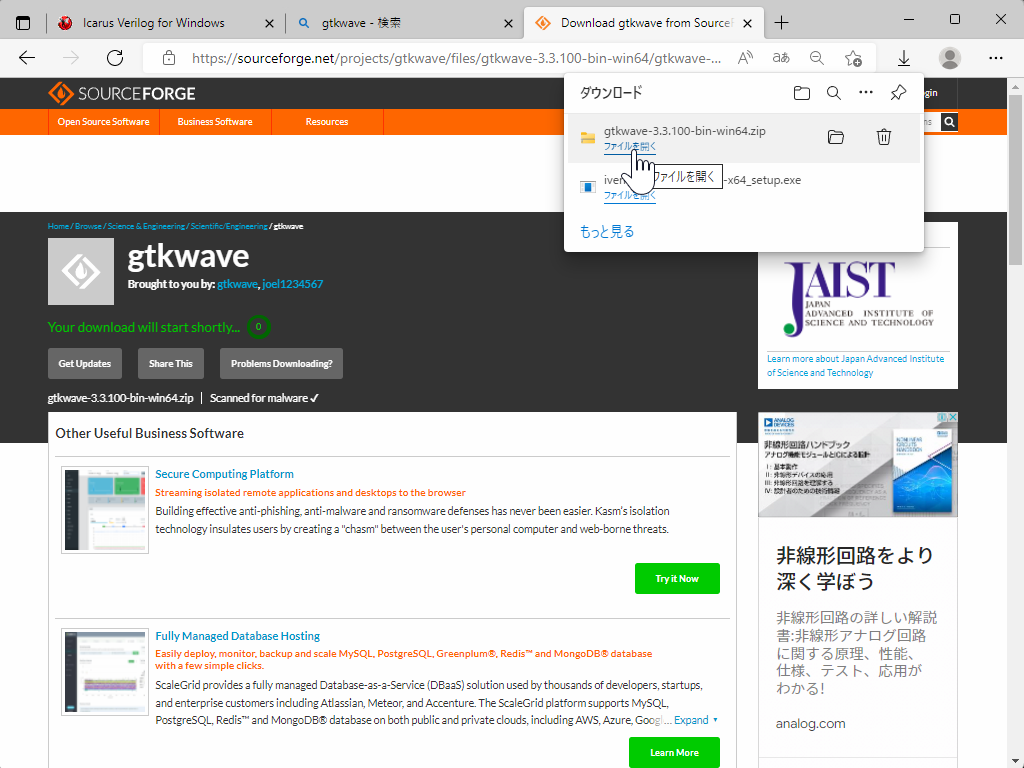

ダウンロードします。

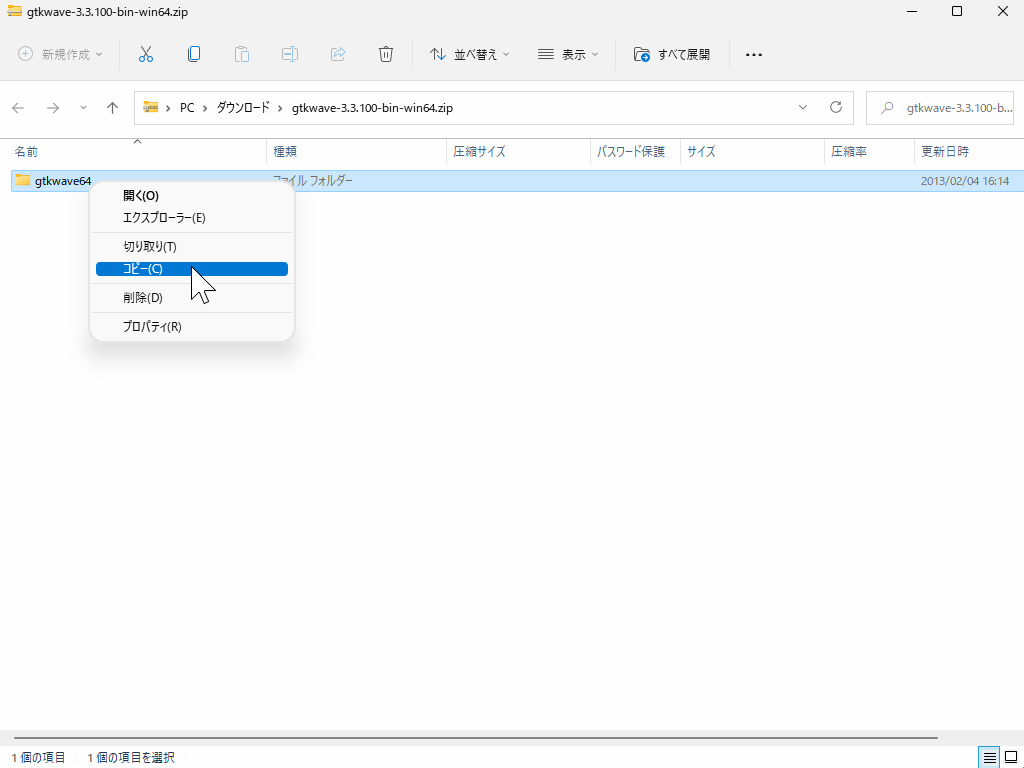

ダウンロードがおわるとファイルを開きます。

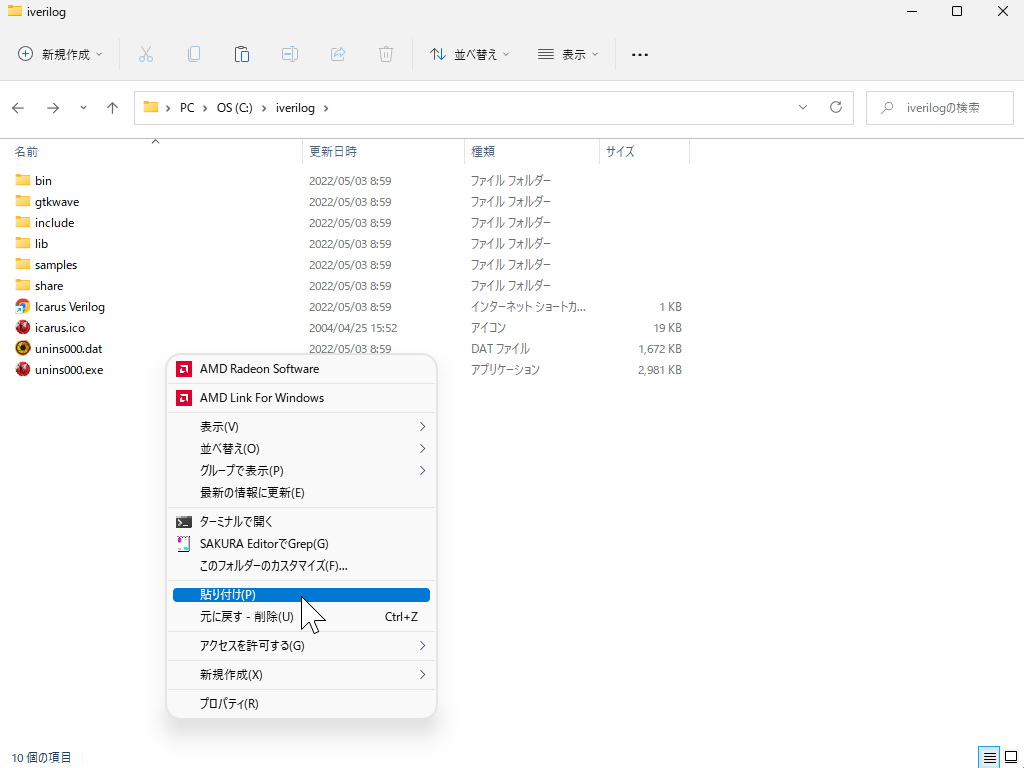

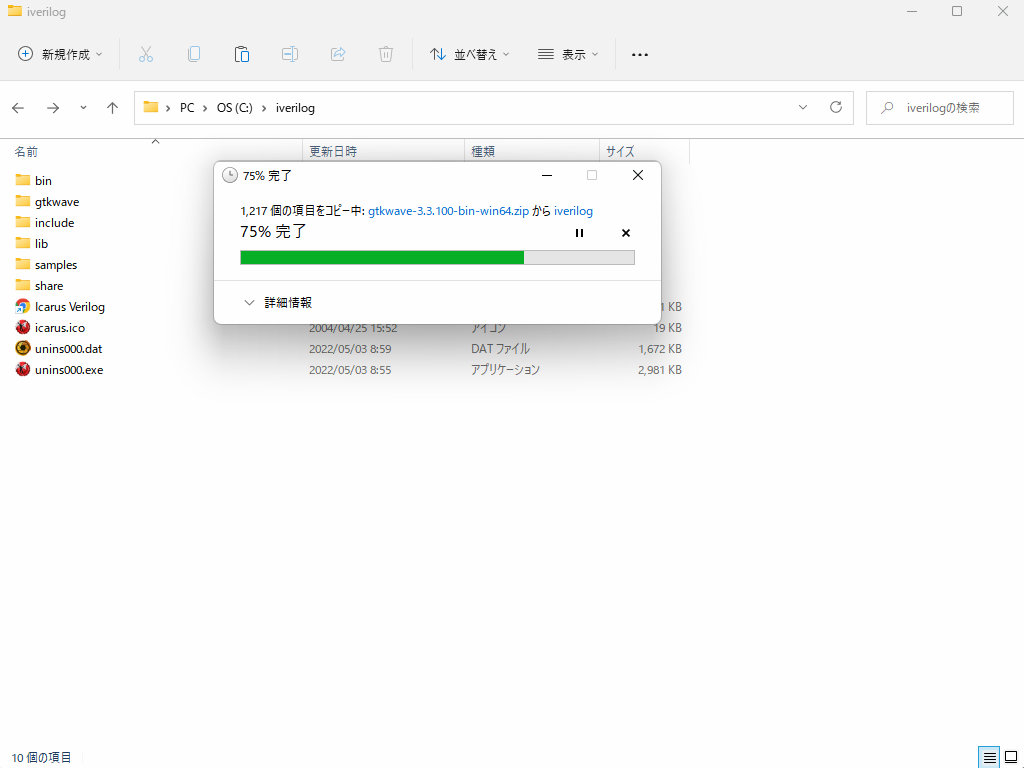

iverilogのインストールされているフォルダに解凍します。

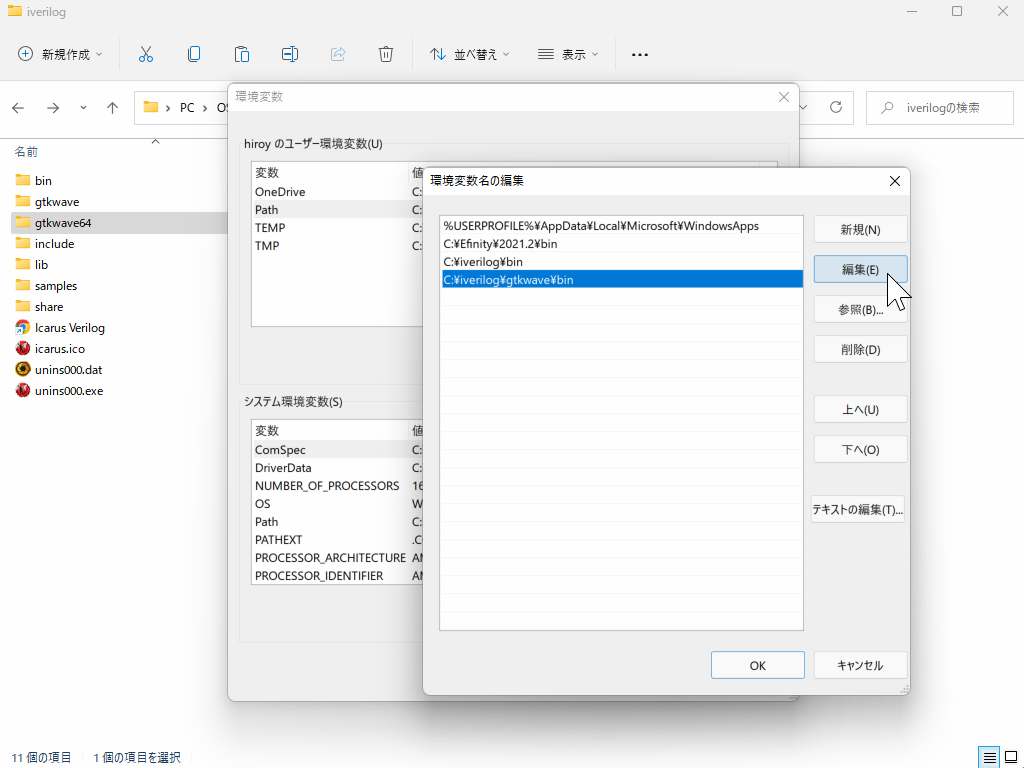

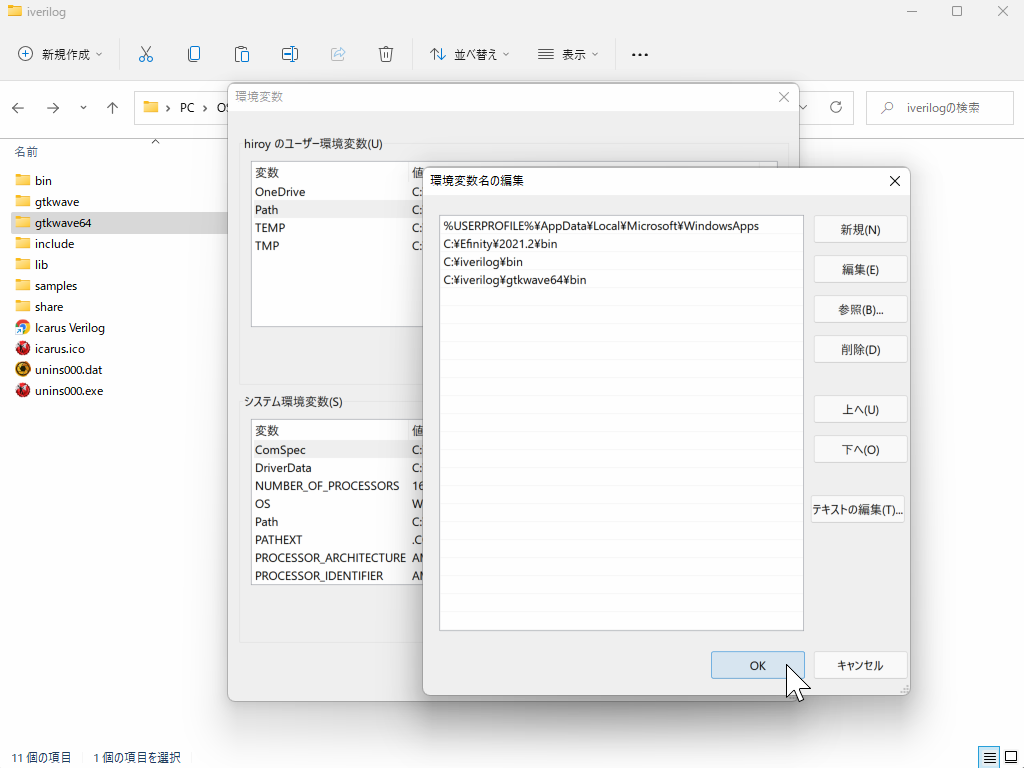

環境変数をgtkwave\binを先ほど解凍したgtkwave64\bin変更します。

PCを再起動して、GTKwaveを起動します。

バージョンが3.3.100になっています。