XILINX(ISE) カスタム AXI-Master IPのシミュレーション

作成者:mou-mou

AXIマスターオリジナルIPを製作する為に、Xilinx社提供のサンプルコードでのシミュレーションをご紹介します。

本来は、Xilinx社より提供されるAXI Bus Functional Model (BFM)を使用すれば良いのですが、こちらは有償となっておりますので、MicroBlazeのIPを接続してシミュレーションする環境をご紹介いたします。

プロジェクトの方針

- ISE 14.7を使用する

- Avnet社製MicroBoardに搭載することを前提に進める

- AR# 37425 – 12.3 EDK、12.3 ISE – カスタム AXI IP コアの作成方法のaxi_master_v1_00_aを使用する

- AXI Bus Functional Model (BFM)は使用しない

- プロジェクトの中にEmbedded Processor(MicroBlaze)を含めない

Avnet社製MicroBoardの環境準備

avnet社のホームページよりMicroBoardのXBDを入手します。

EDK 14.3 XBD/IP-XACT Files : avnet_edk14_3_xbd_files_9_11_2012_spartan.zip

http://www.em.avnet.com/en-us/design/drc/Pages/Xilinx-Spartan-6-FPGA-LX9-MicroBoard.aspxのSupport and Downloadsから入手できます。

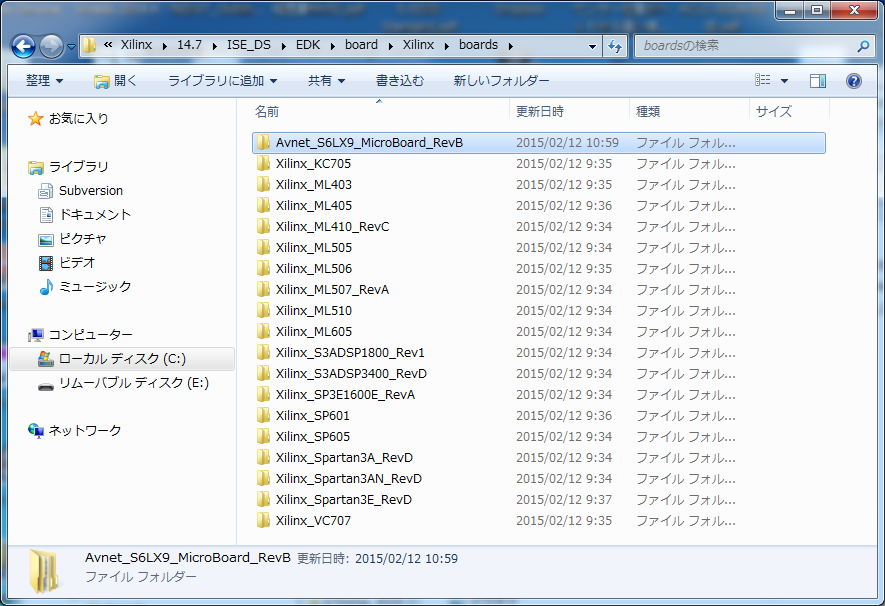

avnet_edk14_3_xbd_files.zip/boards/Avnet_S6LX9_MicroBoard_RevBを/Xilinx/14.7/ISE_DS\EDK/board/Xilinx/boardsにコピーします。

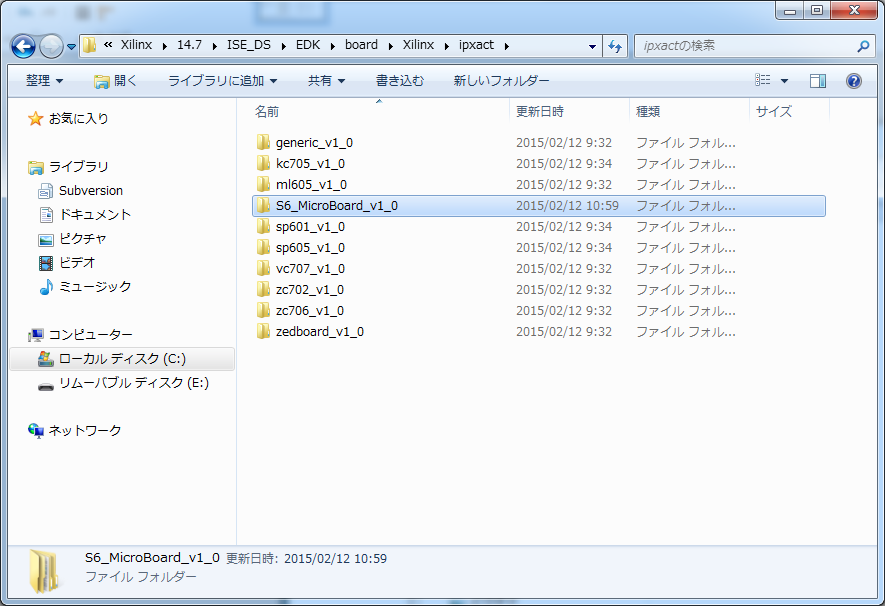

avnet_edk14_3_xbd_files.zip/ipxact/S6_MicroBoard_v1_0を/Xilinx/14.7/ISE_DS\EDK/board/Xilinx/ipxactにコピーします。

MicroBoardプロジェクトの作成

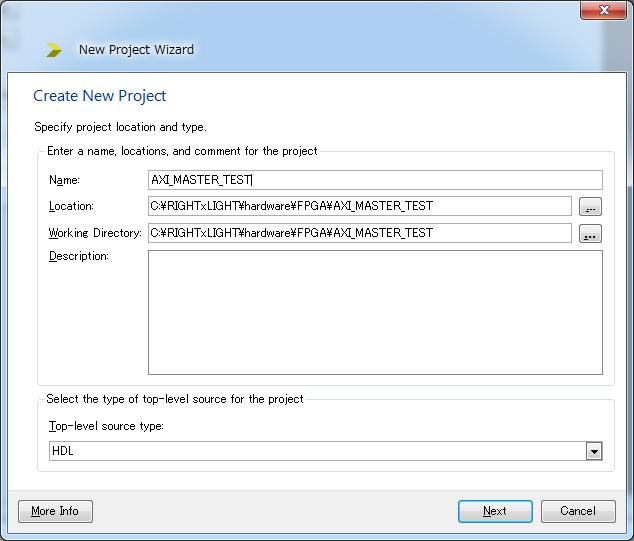

ISEプロジェクトを作成します。

Evaliation Development BoardにAvnet S6LX9 MicroBoard RevBを選択します。

その他は変更せずにfinishまで進めます。

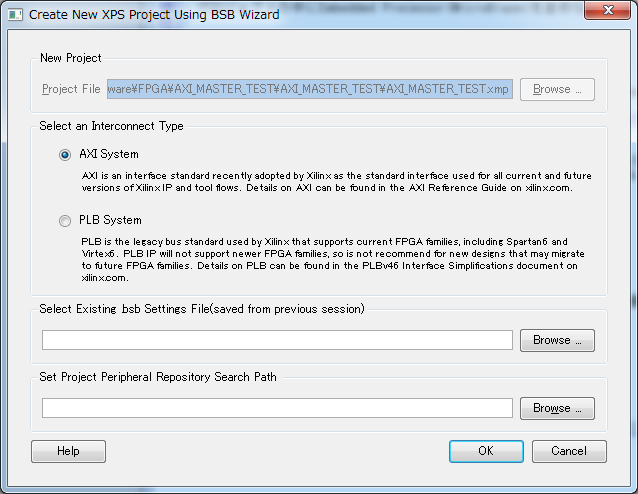

XPSプロジェクトの作成

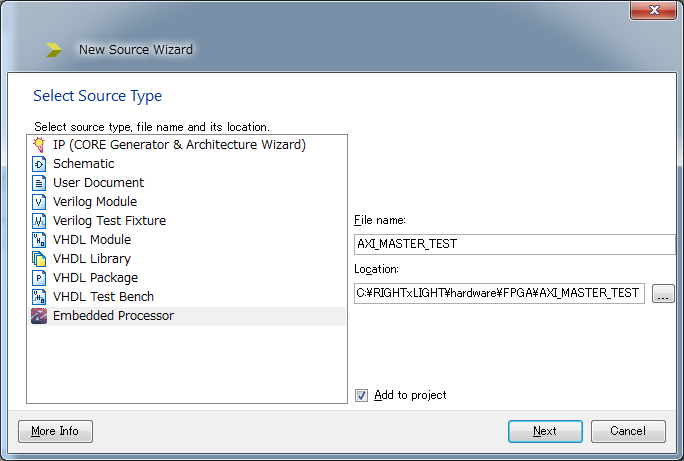

New Source WizardでISEプロジェクトに新しくEmbedded Processorを追加します。

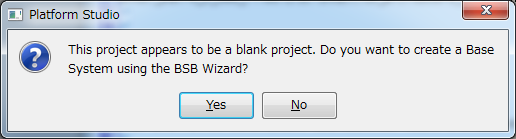

New Source Wizardをfinishまで進めると、XPSが起動しBSB Wizardの使用を確認されるので、Yesを選択します。

AXI Systemがデフォルトで選択されていますので、そのまま次に進みます。

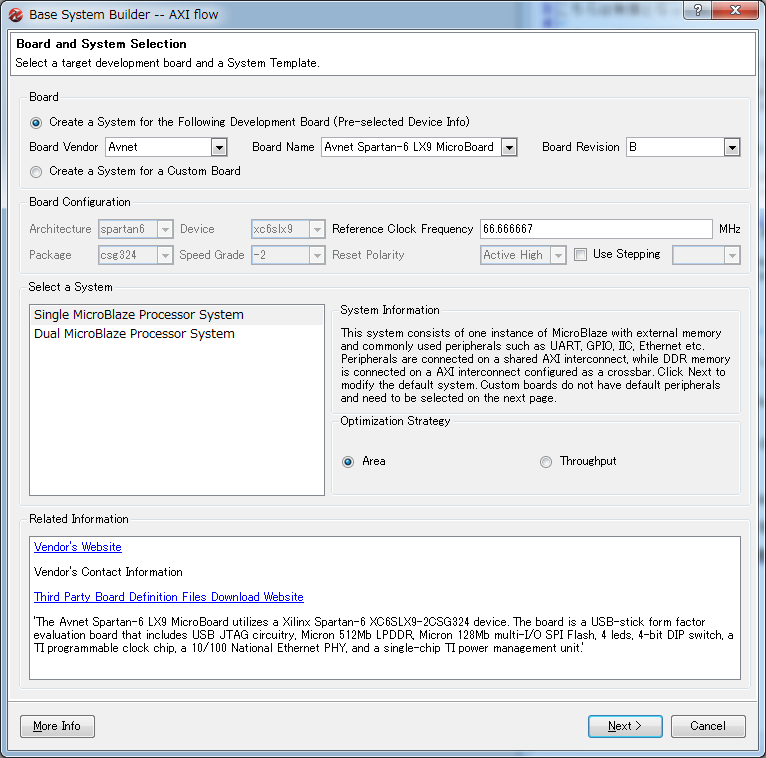

BoardおよびSystemに関する設定はデフォルトのままで次に進みます。

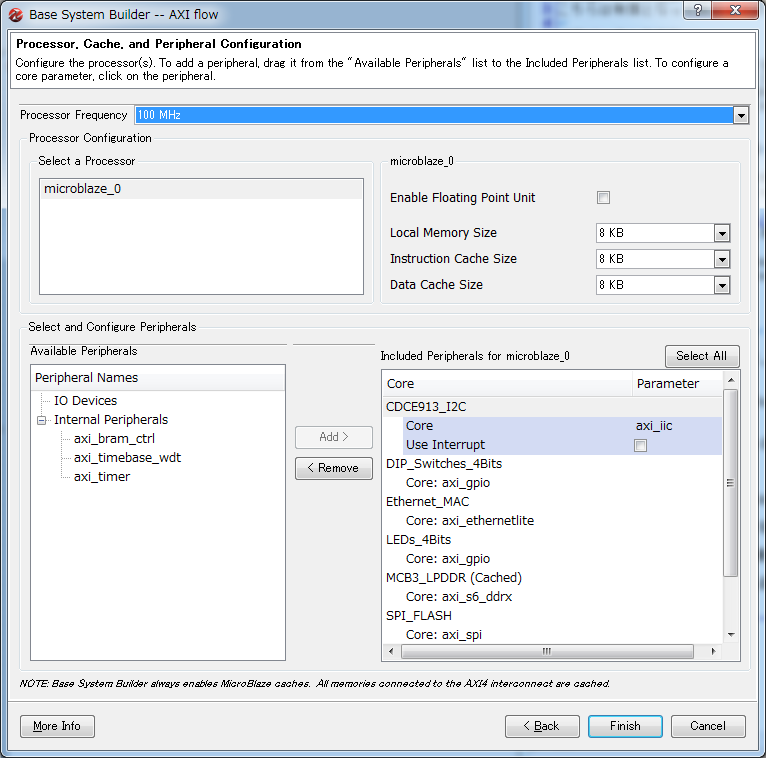

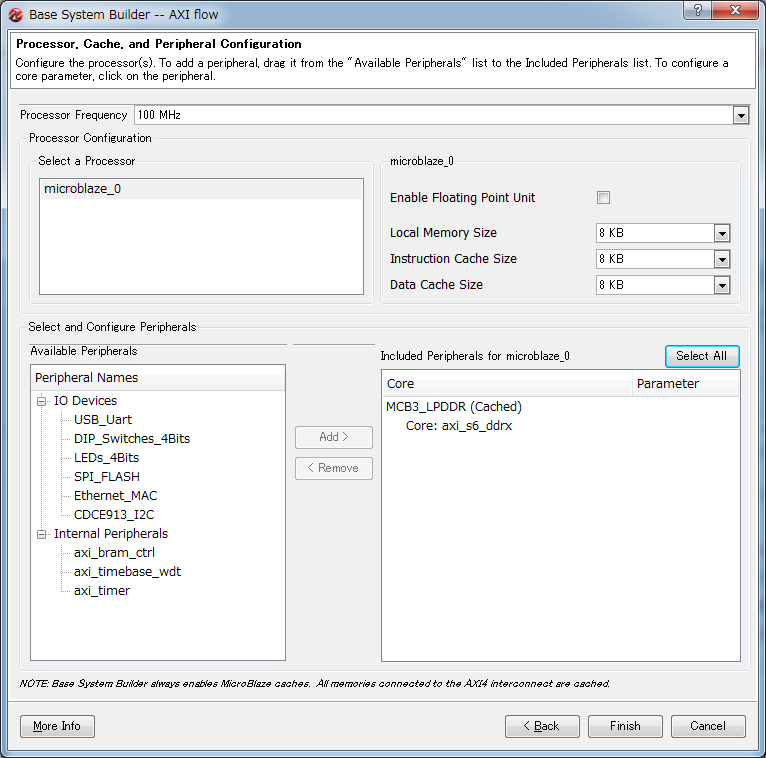

processorとperipheralに関する設定です。

今回は、AXI-MASTERのシミュレーションに特化しますので不要なペリフェラルをすべて削除します。MCB3_LPDDR(Cached)以外はすべてRemoveして、Finishします。

XPSプロジェクトへのAXI-Master IPの追加

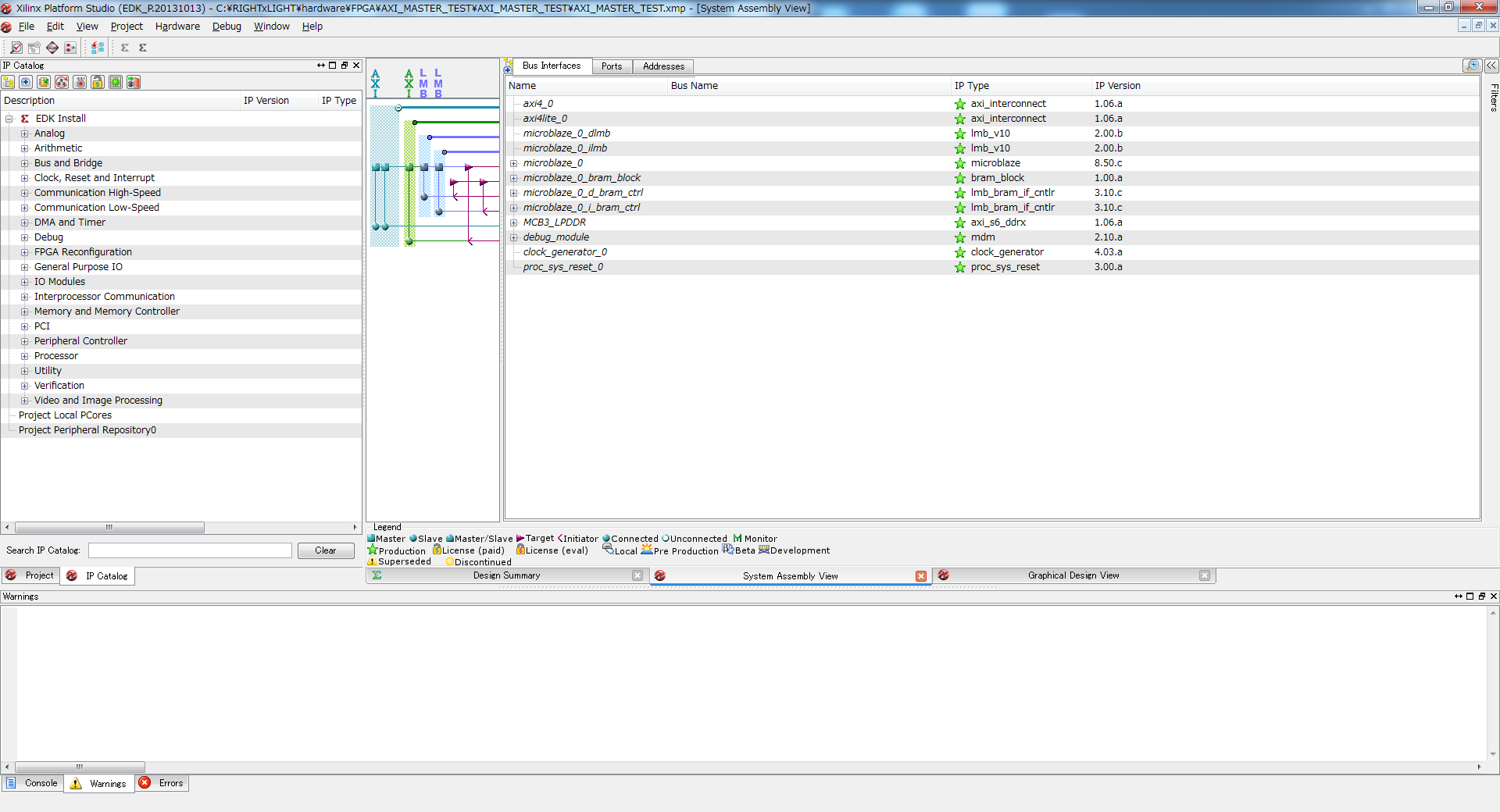

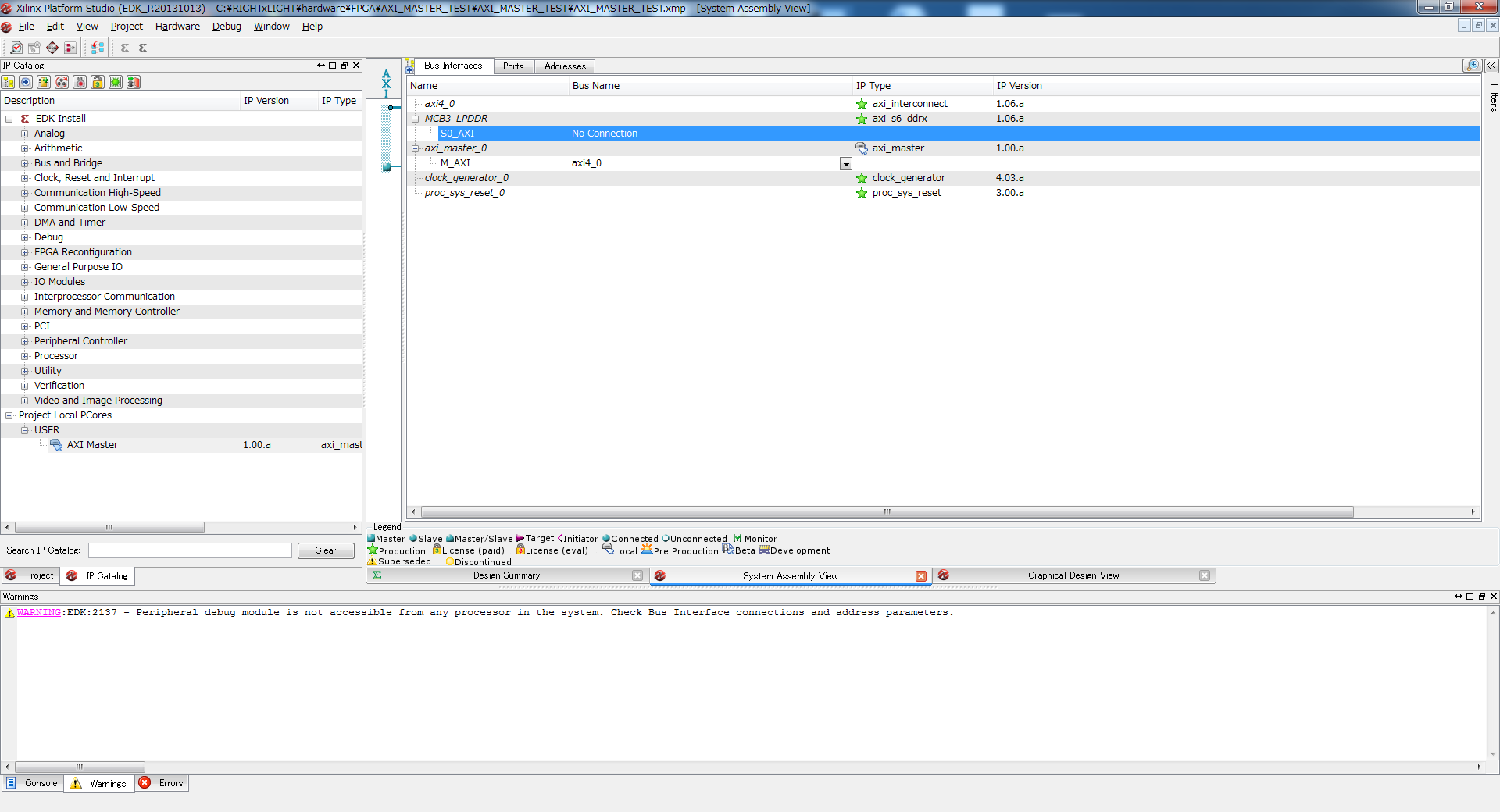

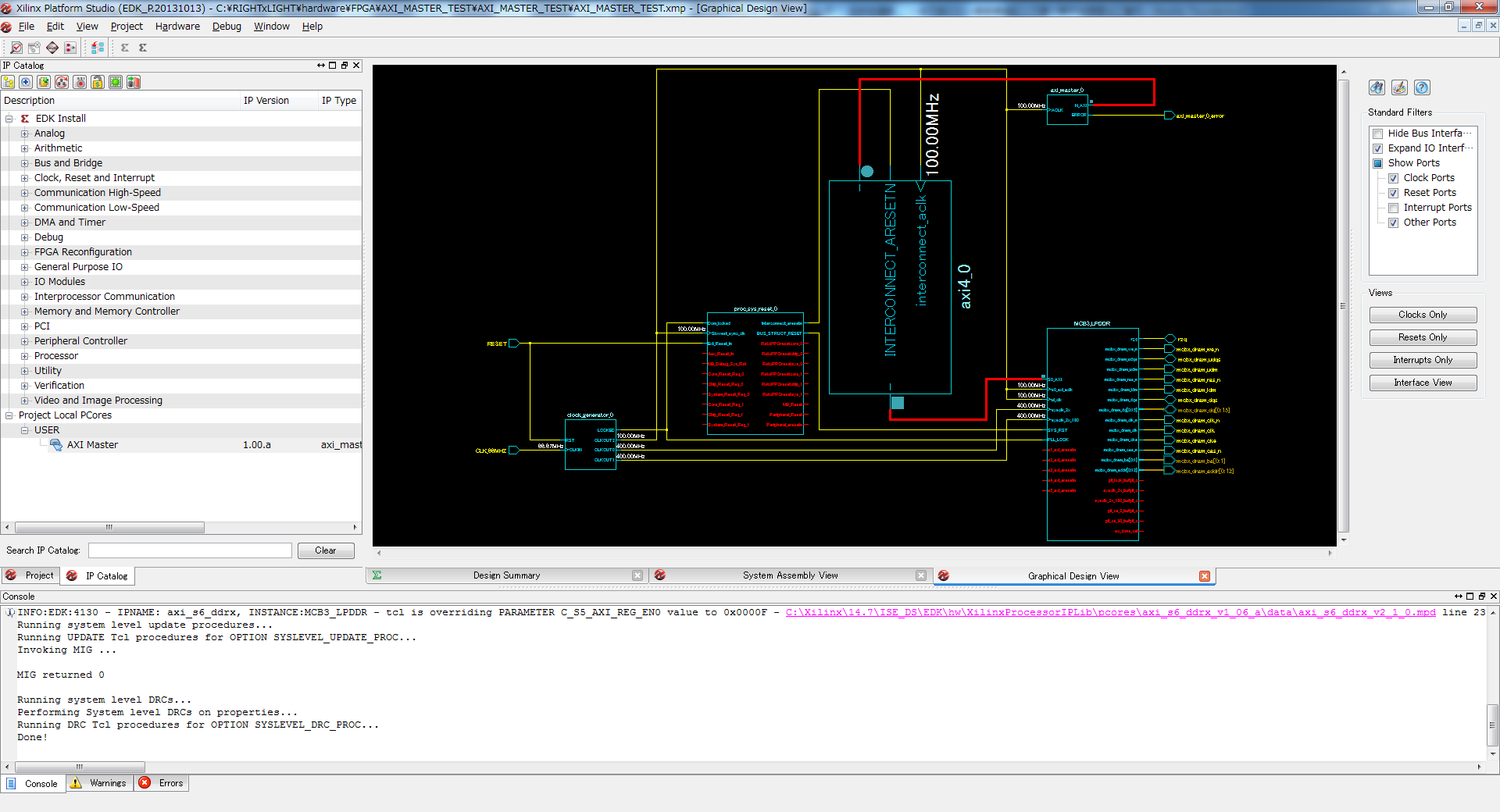

BSB Wizardが終了するとXPSが起動します。

今回は、AXI-MASTERのシミュレーションに特化しますのでaxilite_0とmicroblaze関連のIP及びdebug_moduleを削除します。

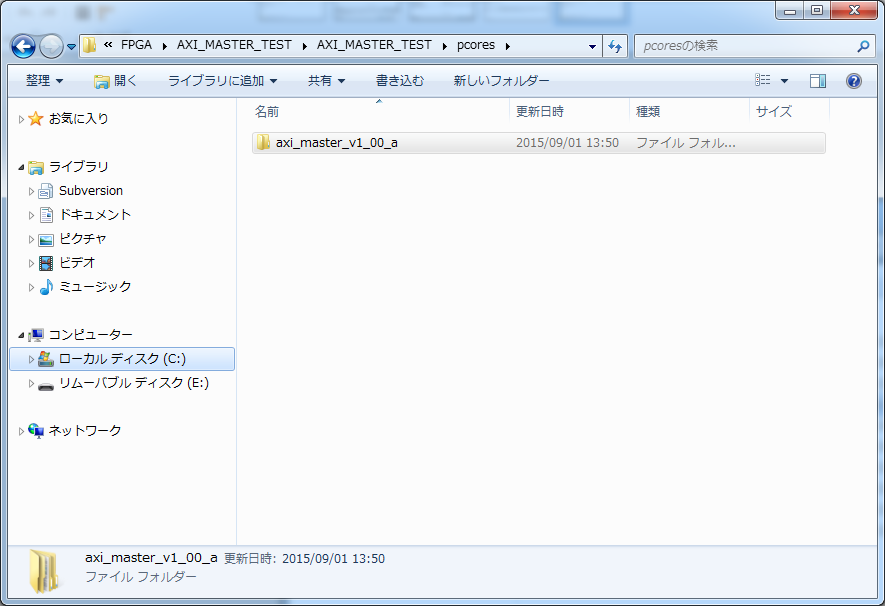

AR37425.zipをxilinx社のホームページからダウンロード-解凍して、axi_master_v1_00_aフォルダをAXI_MASTER_TEST/AXI_MASTER_TEST/pcoresにコピーします。

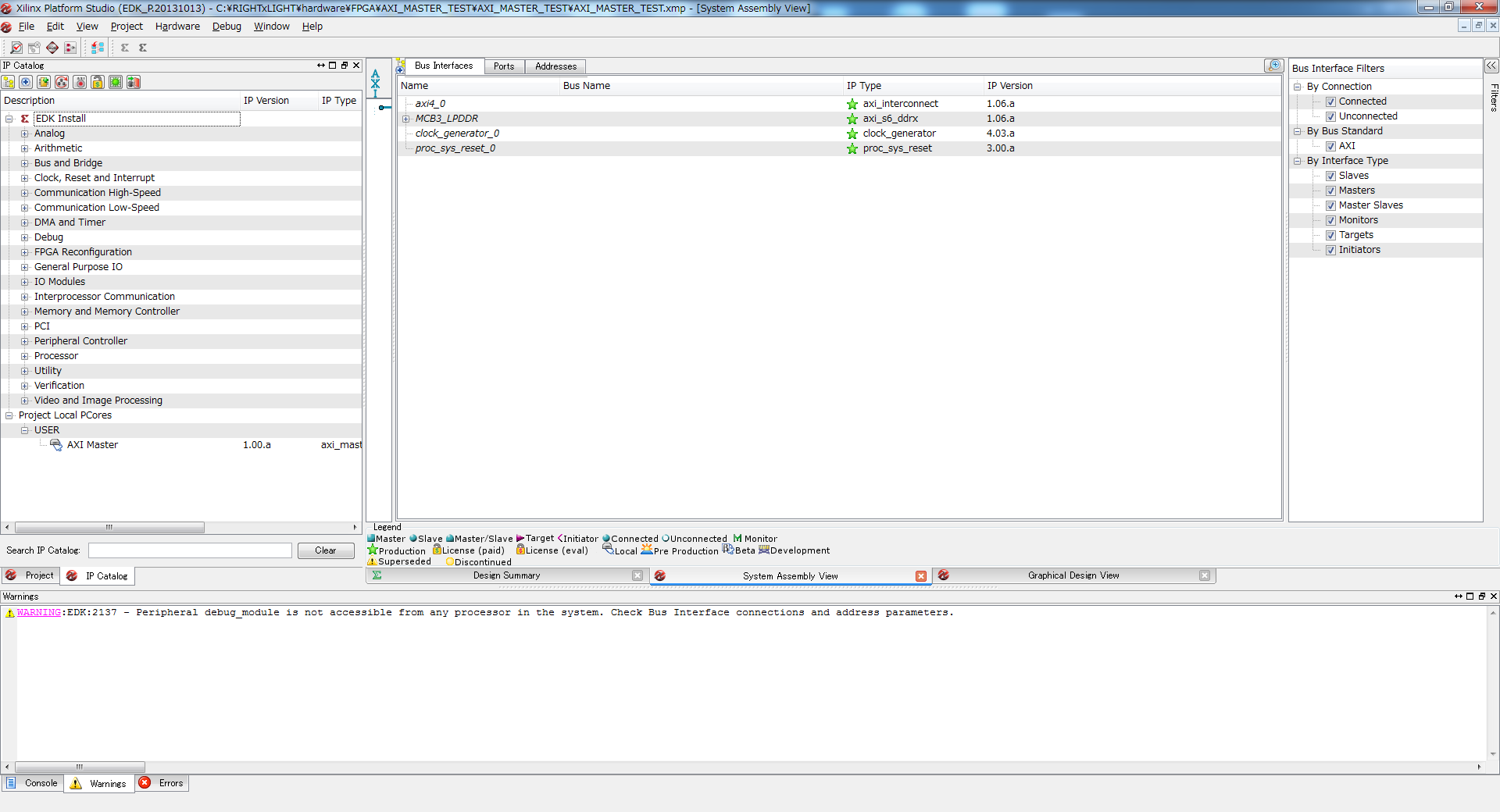

Project->Rescan User Repositoriesをクリックすると、IP CatalogにAXI Masterが追加されます。

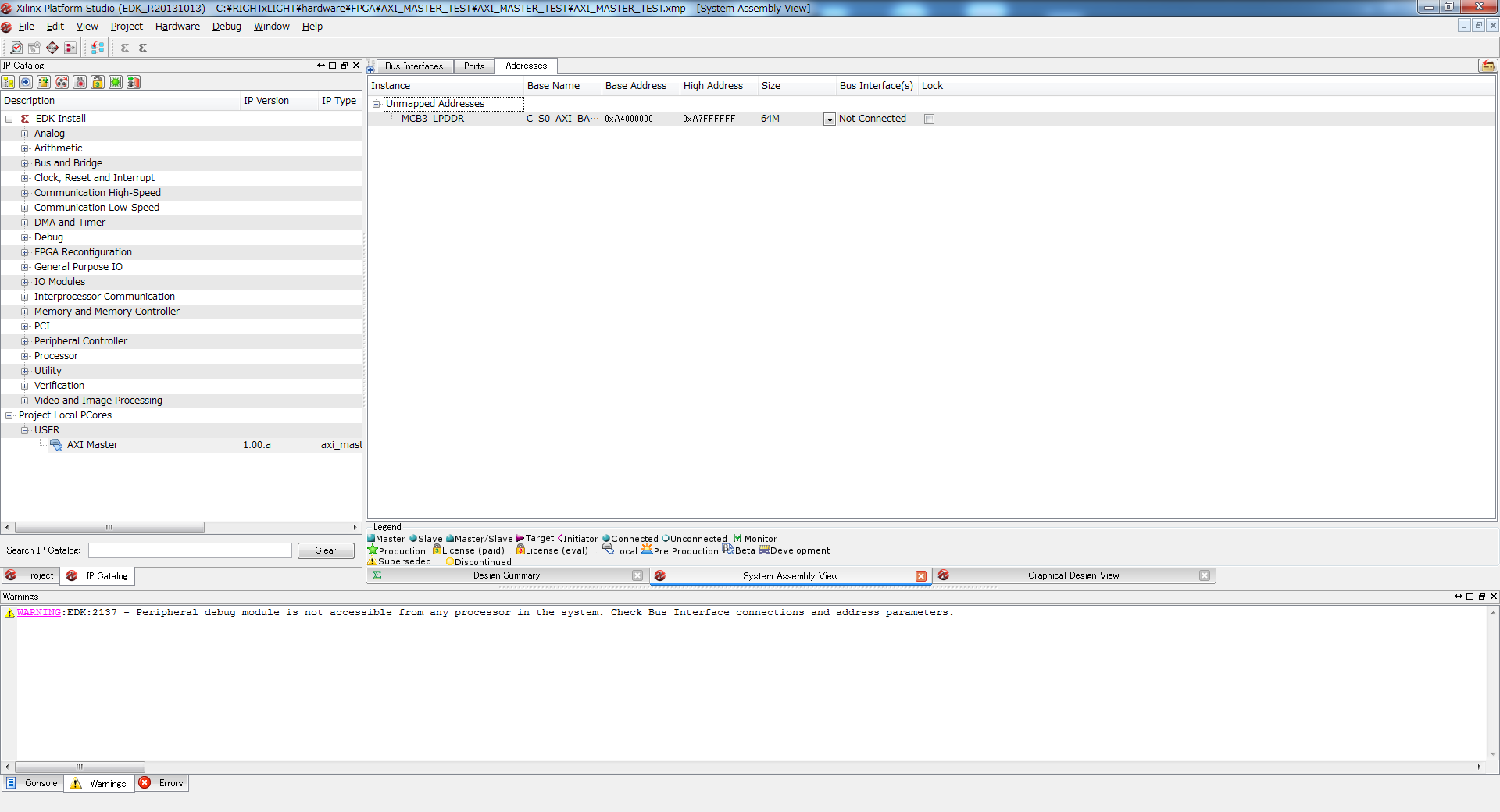

MCB_LPDDRのAddressを確認します。0xA4000000-0xA7FFFFFFになっています。

Project->Rescan User Repositoriesをクリックすると、IP CatalogにAXI Masterが追加されます。

AXI Master IPを追加します。

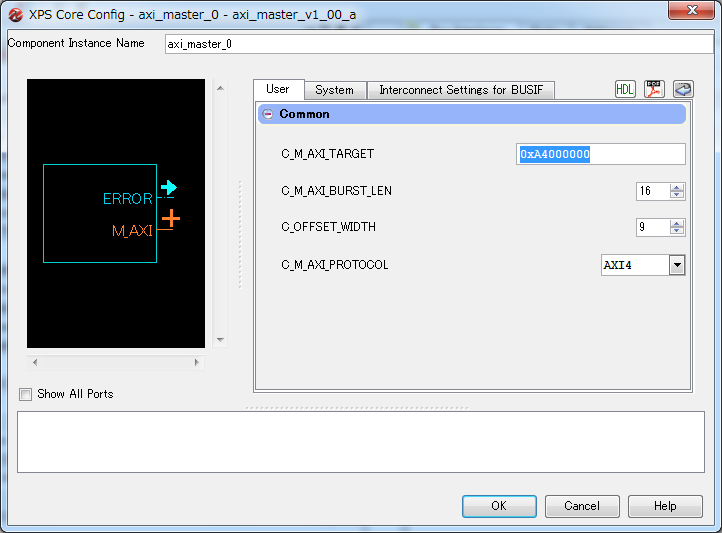

C_M_AXI_TARGETは、前項で確認したMCB_LPDDRの先頭アドレスである0xA4000000を設定します。

C_M_AXI_BURST_LENは、AXIのバースト長を指定します。今回はディフォルトのままにします。

C_OFFSET_WIDTHはサンプルの書き込み範囲のビット数を示しております。初期値は9になっていますので0xA4000000から0xA40001FFまでの512バイトのWrite/Readテストを行います。

C_M_AXI_PROTOCOLはAXI(ディフォルト値)とします。

その他は変更不要です。

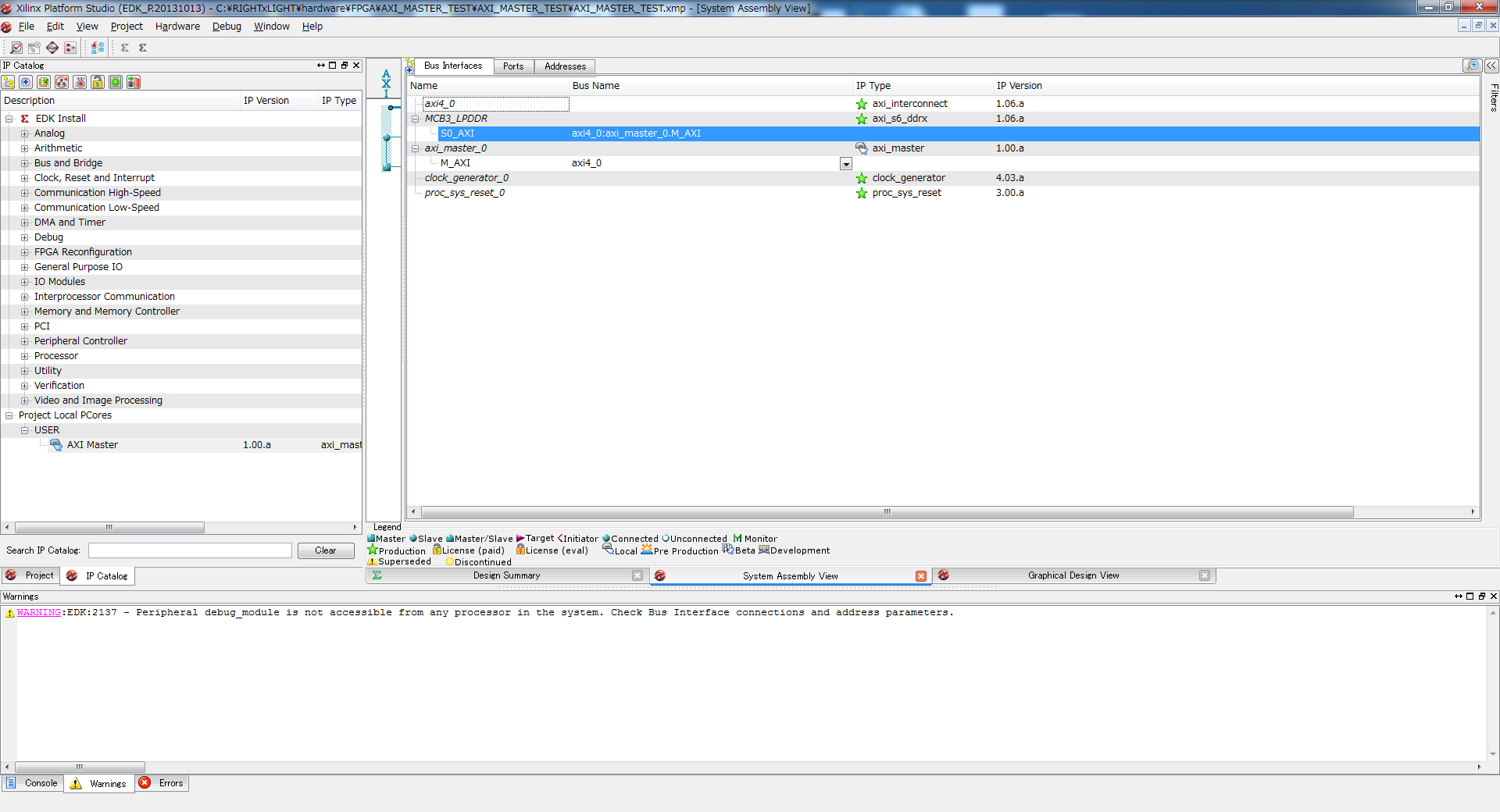

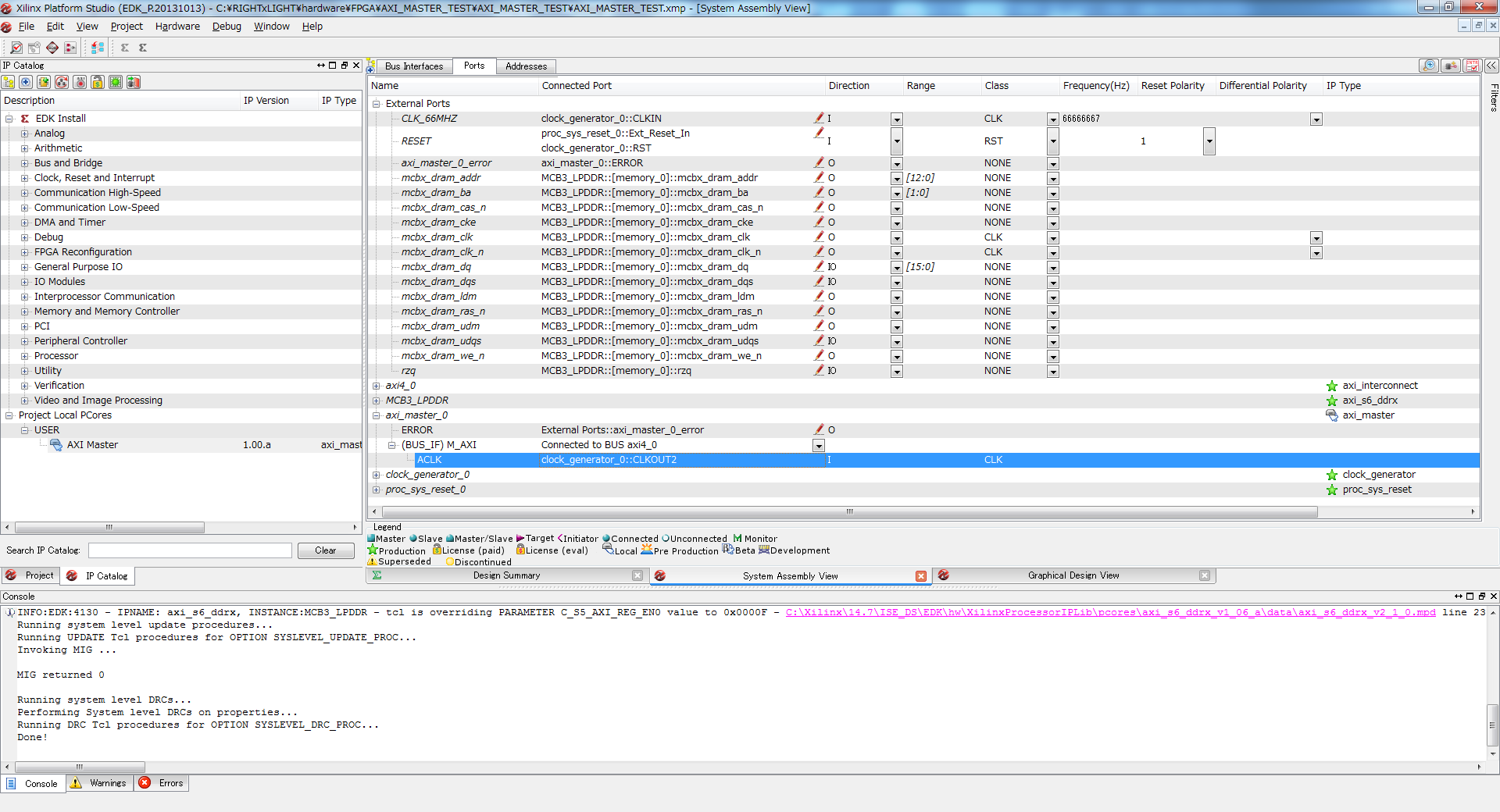

axi_master_0が追加されますので、axi_master_0をaxi4_0にバス接続します。

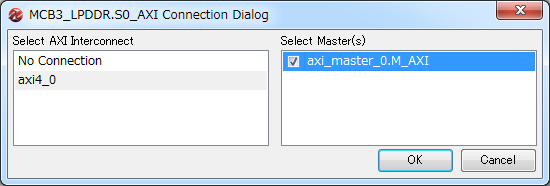

MCB3_LPDDRをaxi4_0にバス接続します。

これで、axi_master_0とMCB3_LPDDRがAXI4で接続されました。

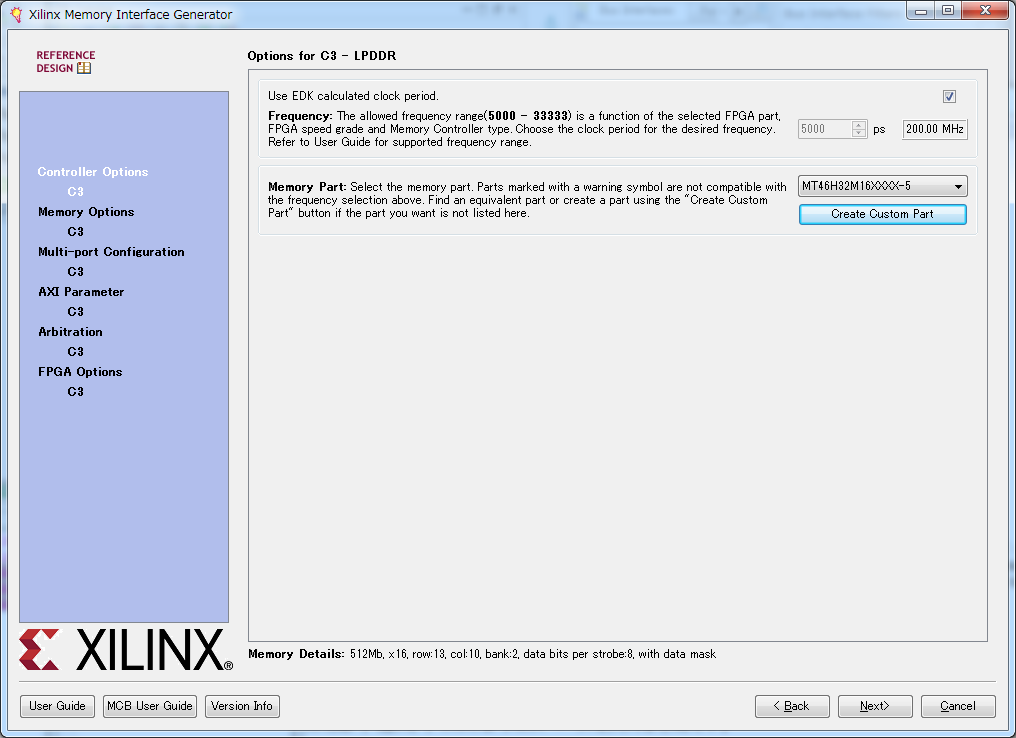

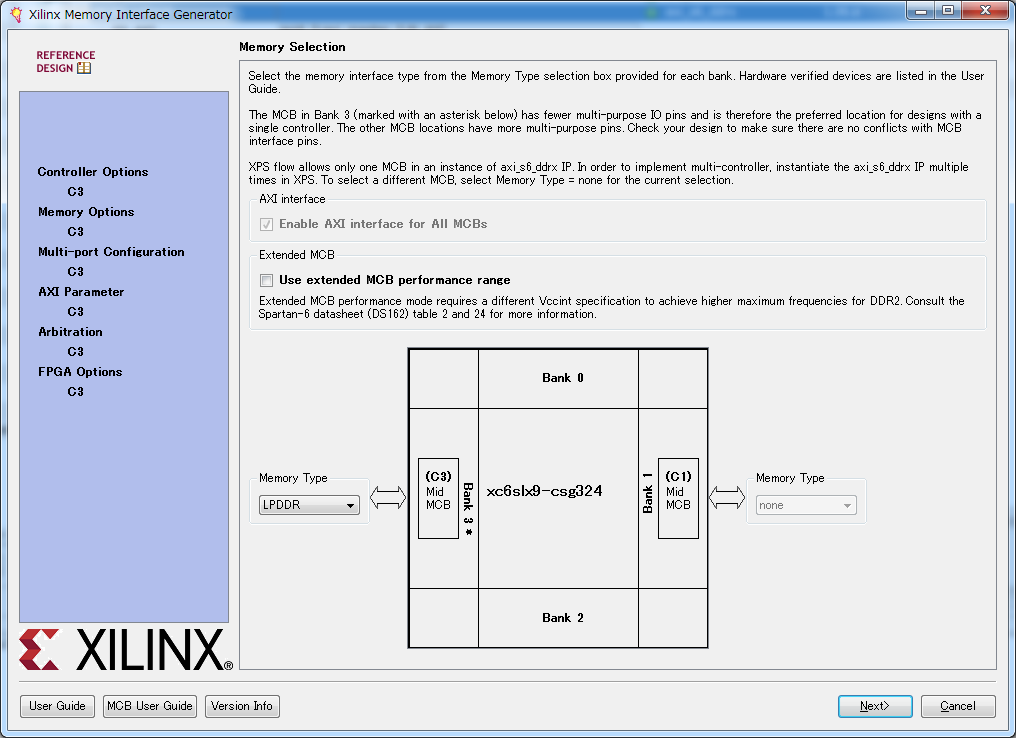

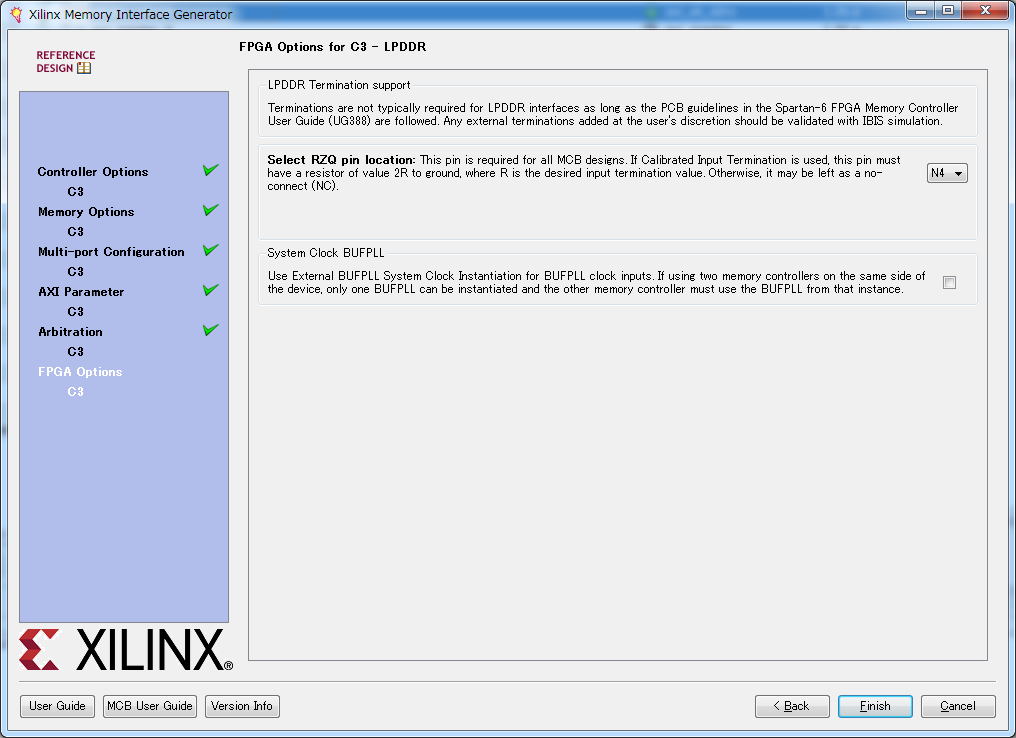

LPDDR SDRAMのシミュレーションモデルを生成する為に、MCB3_LPDDRのMIGを起動します。

設定の変更は必要ありませんので、そのまま進んでいき、finishします。

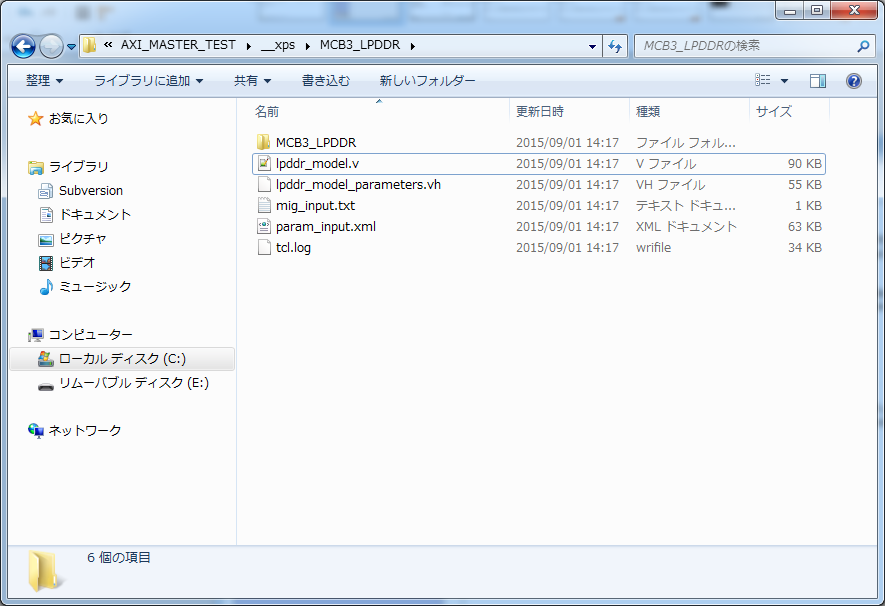

AXI_MASTER_TEST\AXI_MASTER_TEST\__xps\MCB3_LPDDRにLPDDR SDRAMのシミュレーションモデルが生成されます。

axi_master_0のポートを接続します。

- axi_master_0::ERROR – External Ports axi_master_0_error(新規)

- axi_master_0::M_AXI::ACLK – clock_generator_0::CLKOUT2

Graphic Design Viewを確認します。

Design Rule Checkを行いErrorおよびWarningがないことを確認してXPSを終了します。

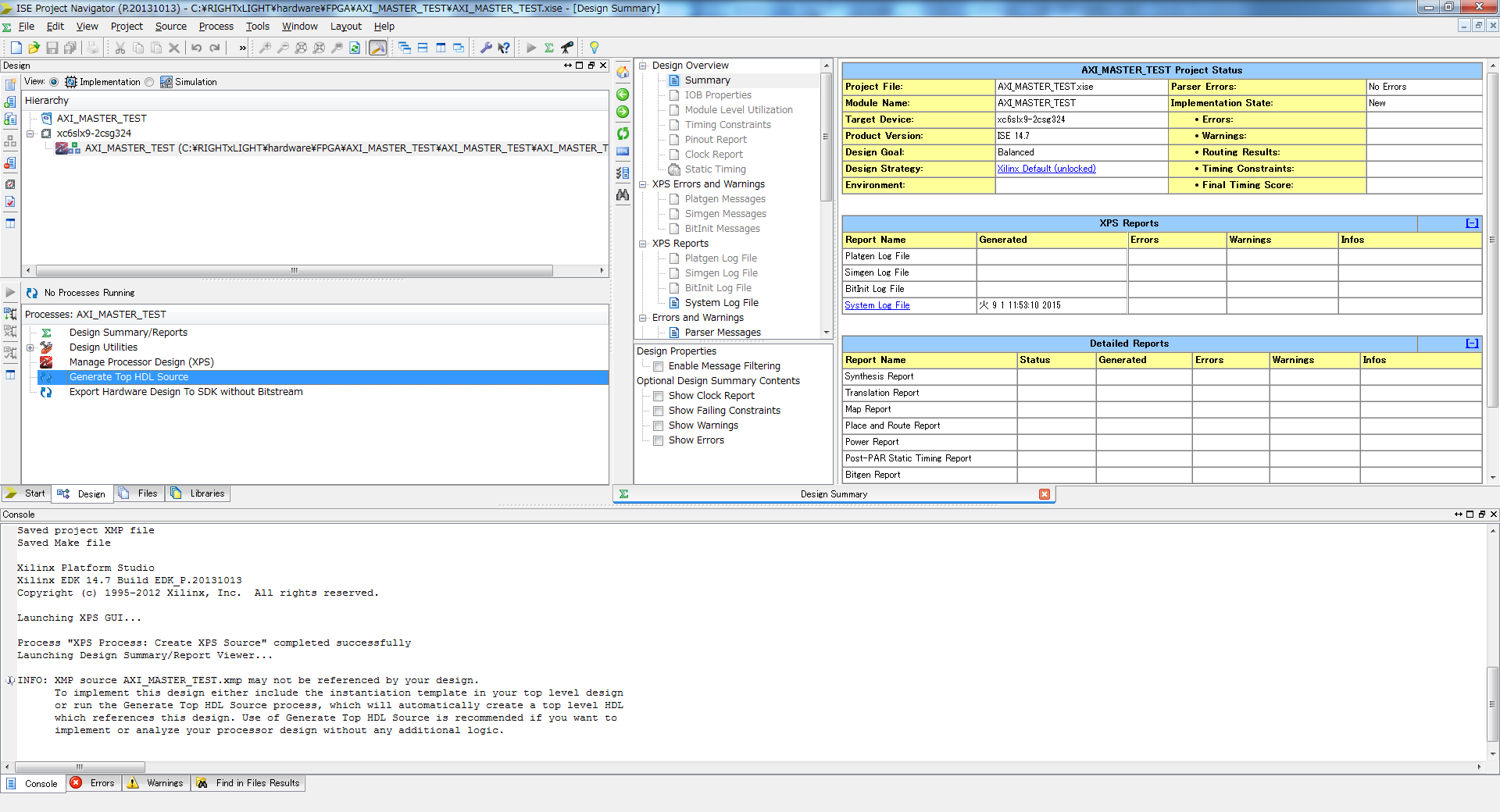

ISEプロジェクトの完成

ISEに戻って、Generate Top HDL Sourceを実行します。

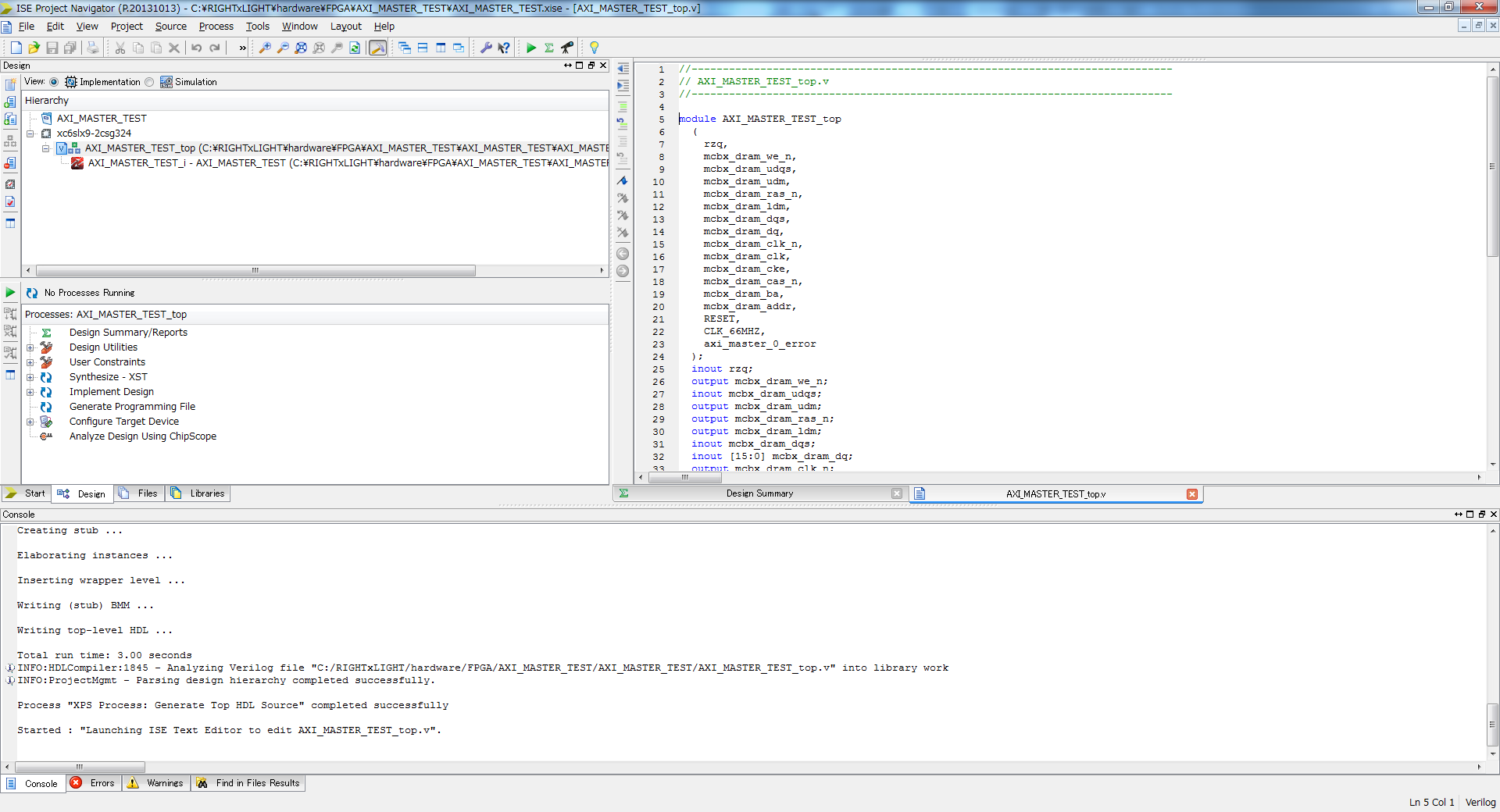

AXI_MASTER_TEST_top.vが生成されます。

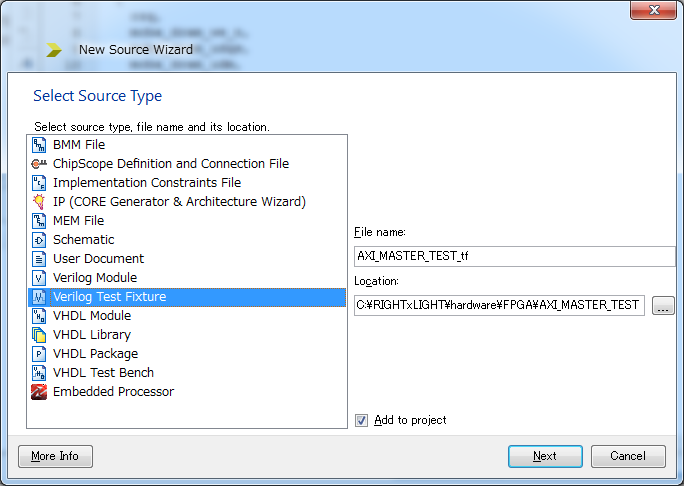

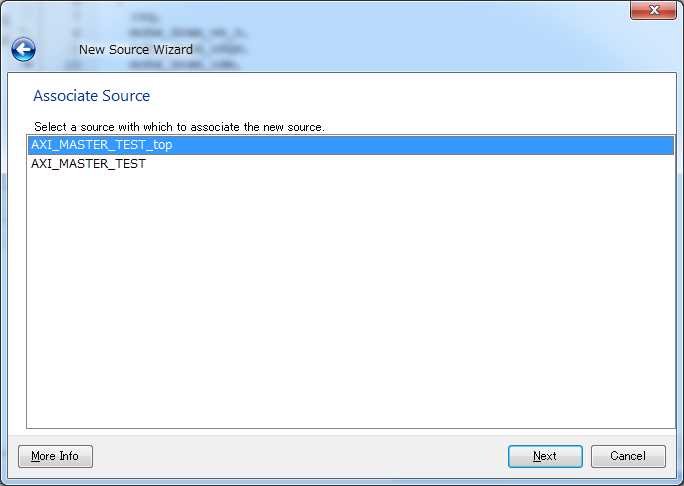

New Source WizardでISEプロジェクトに新しくテストベンチファイルを追加します。

AXI_MASTER_TEST_topを選択します。

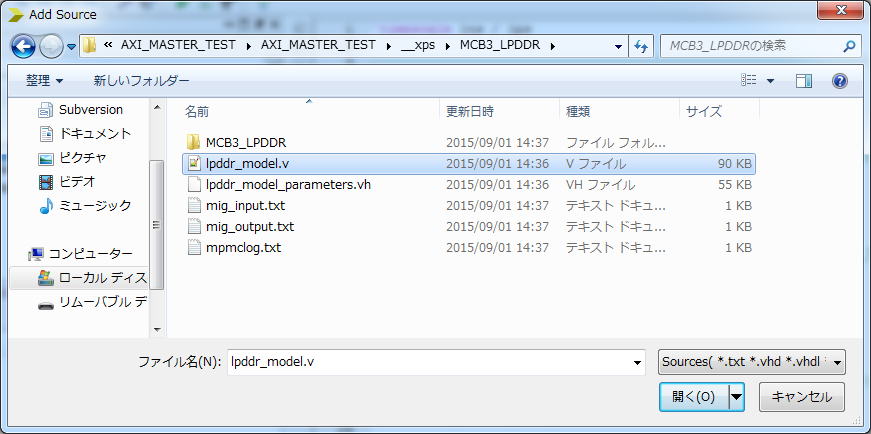

先ほど生成したLPDDR SDRAMのシミュレーションモデル「AXI_MASTER_TEST/AXI_MASTER_TEST/__xps\MCB3_LPDDRのlpddr_model.v」をプロジェクトに追加します。

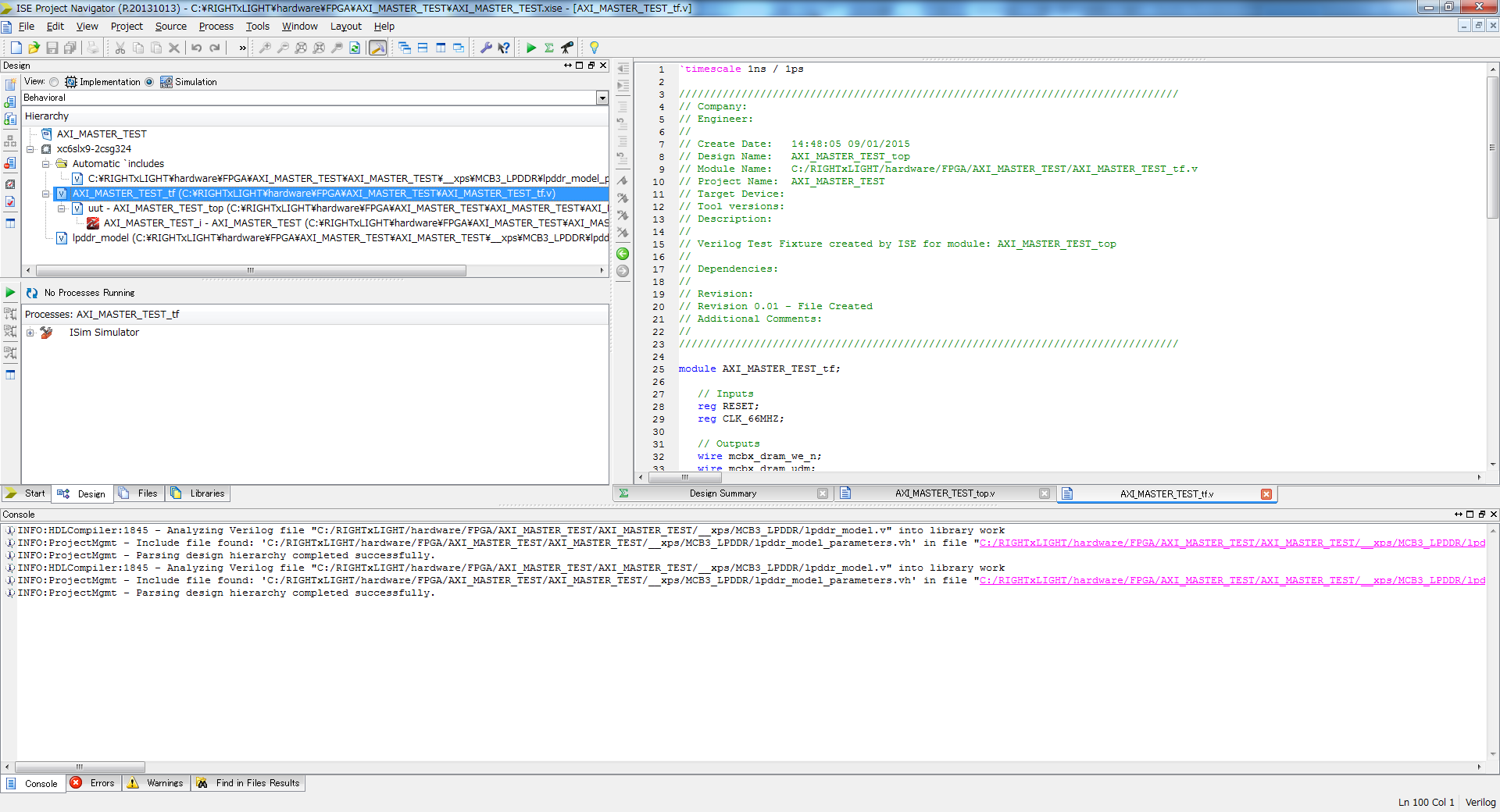

lpddr_modelがプロジェクトに追加されました。

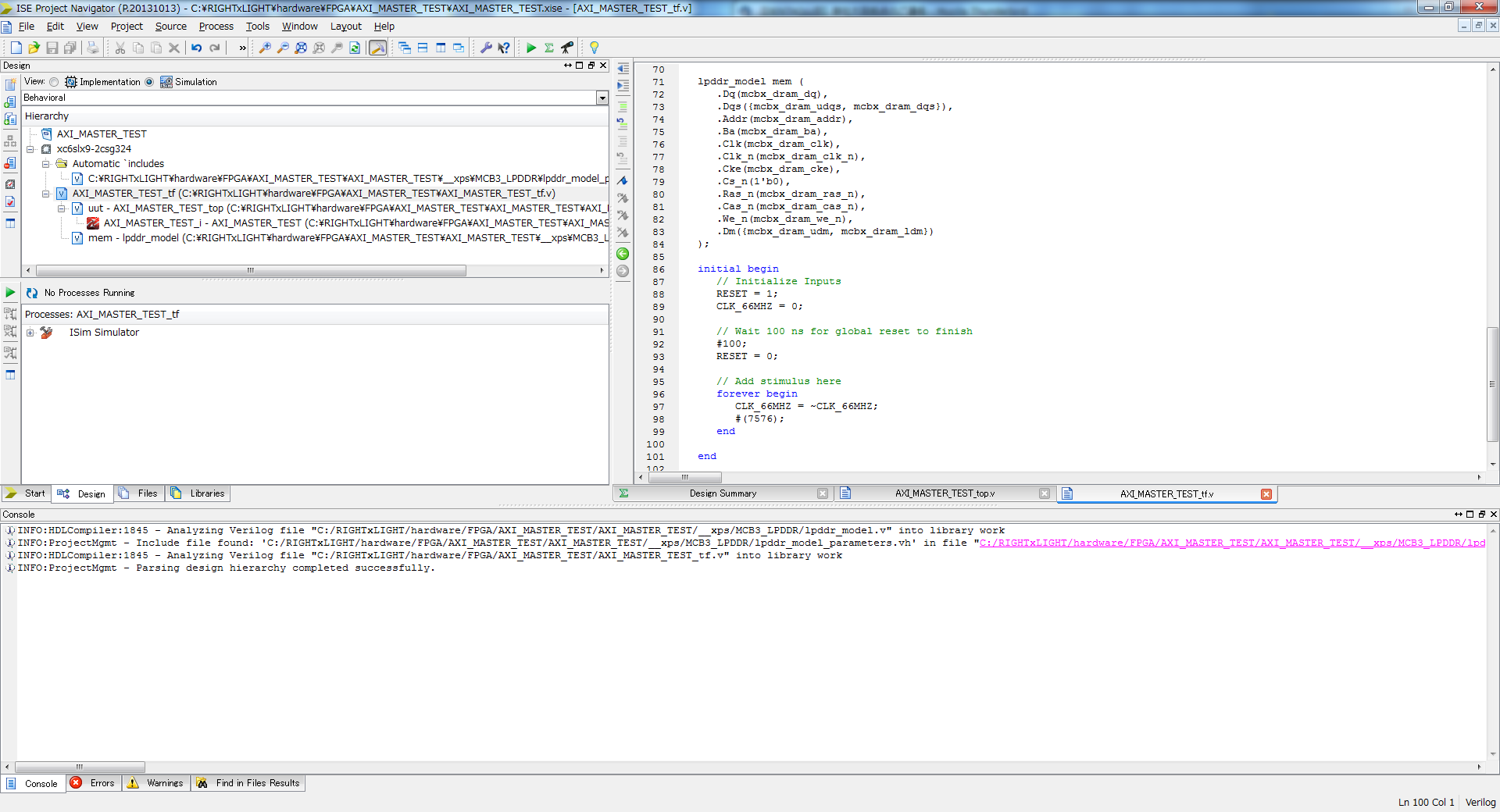

lpddr_modelとの接続等をテストベンチファイルAXI_MASTER_TEST_tf.vに記述します。

【AXI_MASTER_TEST_tf.v】

`timescale 1ps / 1ps module AXI_MASTER_TEST_tf; // Inputs reg RESET; reg CLK_66MHZ; // Outputs wire mcbx_dram_we_n; wire mcbx_dram_udm; wire mcbx_dram_ras_n; wire mcbx_dram_ldm; wire mcbx_dram_clk_n; wire mcbx_dram_clk; wire mcbx_dram_cke; wire mcbx_dram_cas_n; wire [1:0] mcbx_dram_ba; wire [12:0] mcbx_dram_addr; wire axi_master_0_error; // Bidirs wire rzq; wire mcbx_dram_udqs; wire mcbx_dram_dqs; wire [15:0] mcbx_dram_dq; // Instantiate the Unit Under Test (UUT) AXI_MASTER_TEST_top uut ( .rzq(rzq), .mcbx_dram_we_n(mcbx_dram_we_n), .mcbx_dram_udqs(mcbx_dram_udqs), .mcbx_dram_udm(mcbx_dram_udm), .mcbx_dram_ras_n(mcbx_dram_ras_n), .mcbx_dram_ldm(mcbx_dram_ldm), .mcbx_dram_dqs(mcbx_dram_dqs), .mcbx_dram_dq(mcbx_dram_dq), .mcbx_dram_clk_n(mcbx_dram_clk_n), .mcbx_dram_clk(mcbx_dram_clk), .mcbx_dram_cke(mcbx_dram_cke), .mcbx_dram_cas_n(mcbx_dram_cas_n), .mcbx_dram_ba(mcbx_dram_ba), .mcbx_dram_addr(mcbx_dram_addr), .RESET(RESET), .CLK_66MHZ(CLK_66MHZ), .axi_master_0_error(axi_master_0_error) ); lpddr_model mem ( .Dq(mcbx_dram_dq), .Dqs({mcbx_dram_udqs, mcbx_dram_dqs}), .Addr(mcbx_dram_addr), .Ba(mcbx_dram_ba), .Clk(mcbx_dram_clk), .Clk_n(mcbx_dram_clk_n), .Cke(mcbx_dram_cke), .Cs_n(1'b0), .Ras_n(mcbx_dram_ras_n), .Cas_n(mcbx_dram_cas_n), .We_n(mcbx_dram_we_n), .Dm({mcbx_dram_udm, mcbx_dram_ldm}) ); initial begin // Initialize Inputs RESET = 1; CLK_66MHZ = 0; // Wait 100 ns for global reset to finish #100; RESET = 0; // Add stimulus here forever begin CLK_66MHZ = ~CLK_66MHZ; #(7576); end end endmoduleシミュレーションの実効

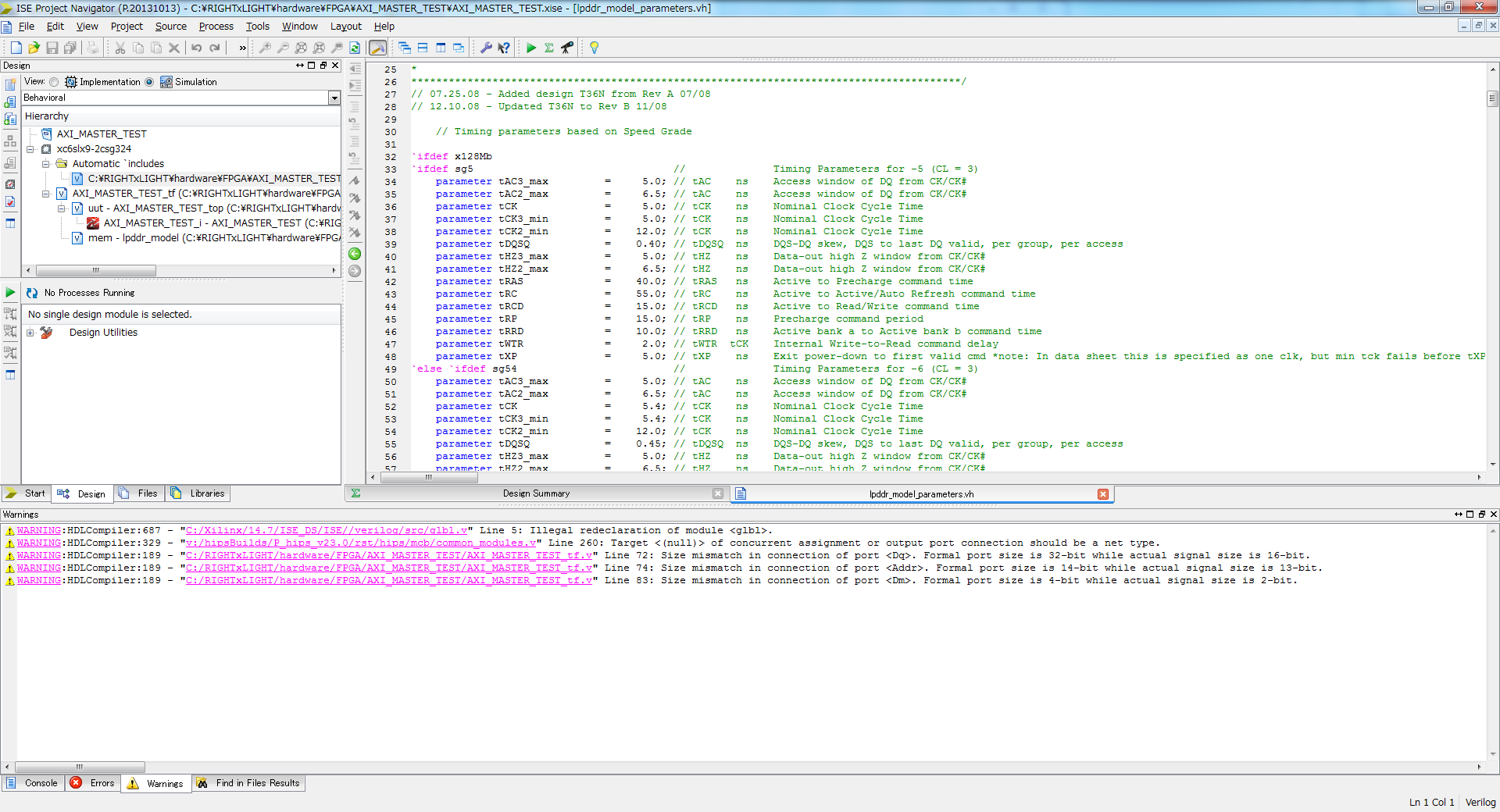

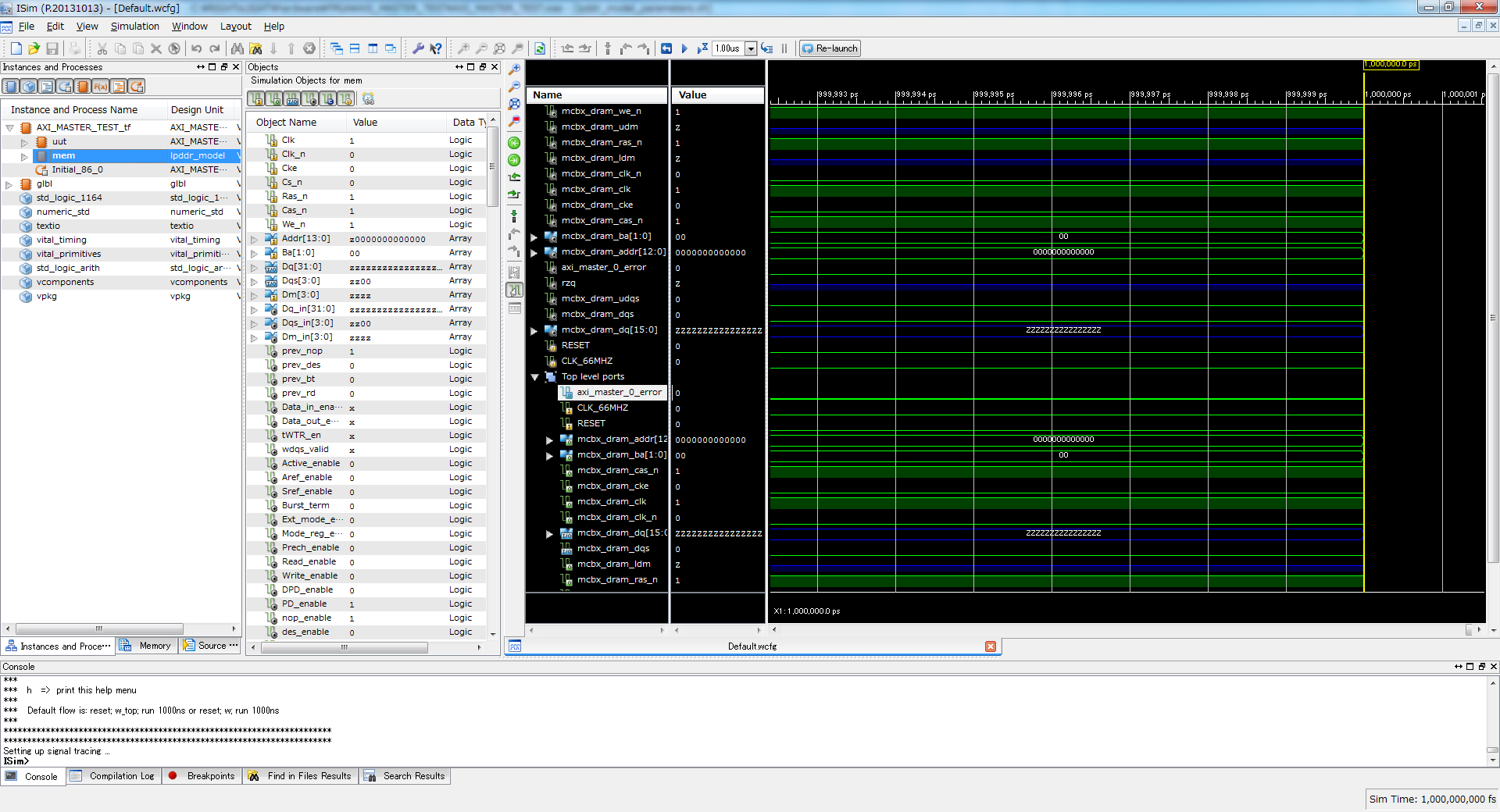

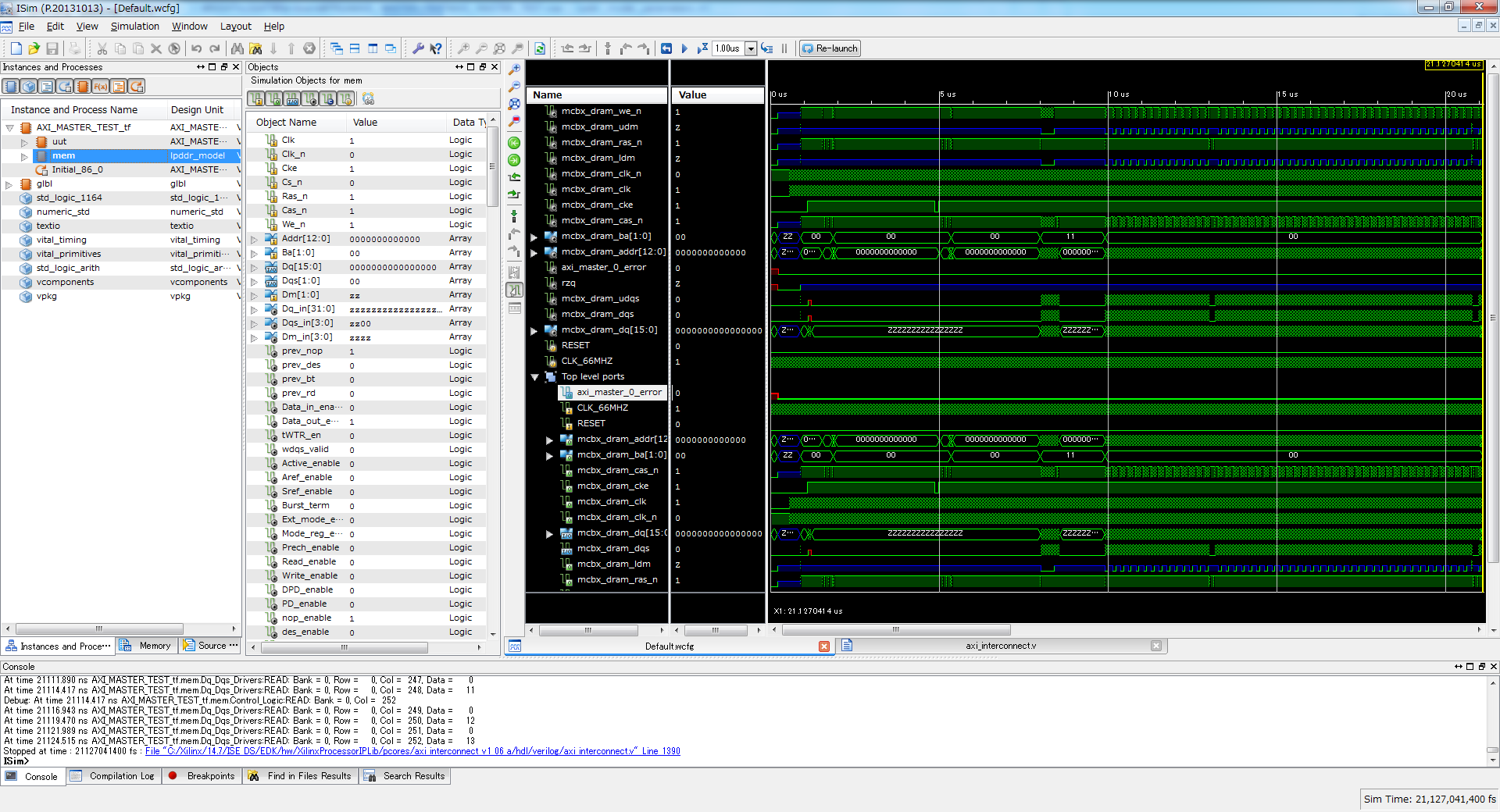

Isim simulatorを実行すると、ワーニングが発生します。

Isimの方を確認しても、確かに、Dq 32ビット, Addr 14ビット, DM 4ビットとなっています。

プロジェクトのAutomatic `includesにあるlpddr_model_parameters.vhを見てみると、メモリ種別に対するifdefがあります。

XPSを再度立ち上げて、MCB3_LPDDRのMIGを起動しすると、MCB3_LPDDRのメモリパートは、MCBMT46H32M16XXXX-5が選択されています。

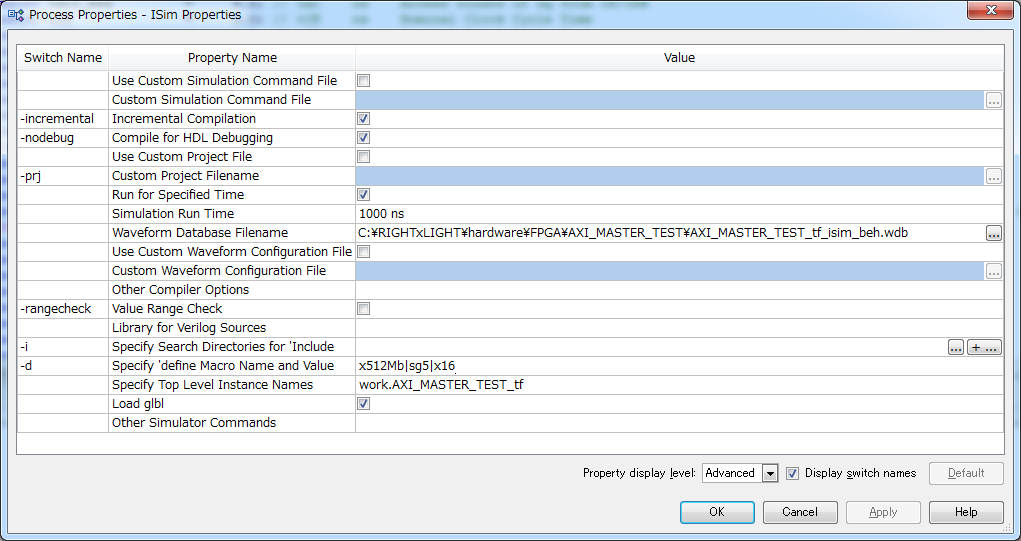

isim Process Propertiesの-d(Specify `define Macro Name and Value)にx512Mb|sg5|x16と入力します。(sg5 = -5 (CL=3))

パラメータは必ず”|”で結合してください。スペースも不可です。

x512Mb sg5 x16

x512Mb | sg5 | x16

これらでは、認識しません。

isimを再起動すると、mem::Addr[12:0] mem::Dq[15:0] mem::Dm[1:0]となり、シミュレーションが成功します。