遅延モジュール(Verilog-HDL / Xilinx)

作成者:mou-mou

弊社のXilinx社製FPGAのRTL開発で使用しております遅延モジュールをご紹介いたします。

パイプラインにおける遅延調整の場合、ロジックの変更によって遅延量の変更が都度発生します。

その度にFFを1段追加あるいは削除するというのは、かなりの面倒な作業と思います。

また、外部入力信号や非同期クロック間転送(CDC)の為のダブルFFシンクロナイザも都度記述するのは、煩わしい作業では無いかと思います。

そこで、ビット幅および遅延量をパラメータ化した遅延モジュールを用意しております。

また、入力ピンおよび出力ピンに直結した場合にIOB内蔵のFFを使用するパラメータも用意しております。

リセットについては、弊社では殆どの場合、同期リセットを使用しておりますが、非同期リセットにも対応できるようにパラメータ化しております。

【delay_ff.v】

//% @file //% @brief delay_ff (for Xilinx FPGA) //% ディレーフリップフロップ module delay_ff # ( parameter DATA_WIDTH = 2, //% データ幅 parameter DELAY_TIME = 3, //% 遅延時間 parameter IFF_USE = 0, //% 初段FF = IOB parameter OFF_USE = 0, //% 最終FF = IOB parameter ARESET_USE = 0 //% 非同期リセット使用 ) ( input CLK, //% クロック input RESET_N, //% リセット(負論理) input [DATA_WIDTH-1:0] IN_DATA, //% 入力データ output [DATA_WIDTH-1:0] OUT_DATA //% 出力データ ); wire [DATA_WIDTH-1:0] data[DELAY_TIME:0]; assign data[0] = IN_DATA; assign OUT_DATA = data[DELAY_TIME]; /*! D-FF */ generate genvar i; for (i = 0; i < DELAY_TIME; i = i + 1) begin : gen_d_ff d_ff #( .DATA_WIDTH(DATA_WIDTH), .IOB_USE((i == 0)? IFF_USE : (i == (DELAY_TIME-1))? OFF_USE : 0), .ARESET_USE(ARESET_USE) ) u_d_ff ( .CLK(CLK), .RESET_N(RESET_N), .IN_DATA(data[i]), .OUT_DATA(data[i+1]) ); end endgenerate endmodule

【d_ff.v】

//% @file

//% @brief d-ff (for Xilinx FPGA)

//% Dタイプフリップフロップ

module d_ff # (

parameter DATA_WIDTH = 1, //% データ幅

parameter IOB_USE = 0, //% IOB使用

parameter ARESET_USE = 0 //% 非同期リセット使用

) (

input CLK, //% クロック

input RESET_N, //% リセット(負論理)

input [DATA_WIDTH-1:0] IN_DATA, //% 入力データ

output [DATA_WIDTH-1:0] OUT_DATA //% 出力データ

);

(* IOB = (IOB_USE)? "TRUE" : "FALSE" *) reg [DATA_WIDTH-1:0] data_reg;

assign OUT_DATA = data_reg;

/*! データレジスタ

*/

generate

if (ARESET_USE) begin

always @(posedge CLK or negedge RESET_N) begin: data_reg_l

if (!RESET_N)

data_reg <= {DATA_WIDTH{1'b0}};

else

data_reg <= IN_DATA;

end

end

else begin

always @(posedge CLK) begin: data_reg_l

if (!RESET_N)

data_reg <= {DATA_WIDTH{1'b0}};

else

data_reg <= IN_DATA;

end

end

endgenerate

endmodule

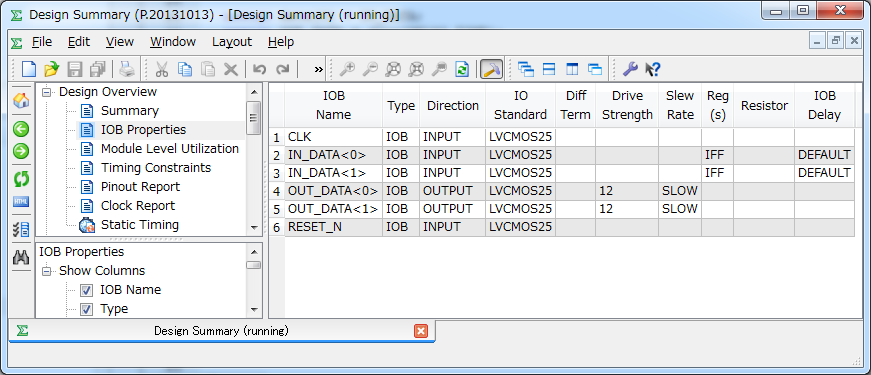

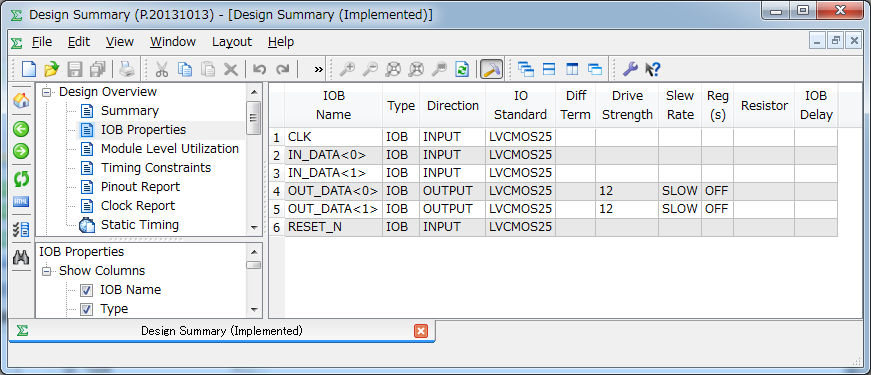

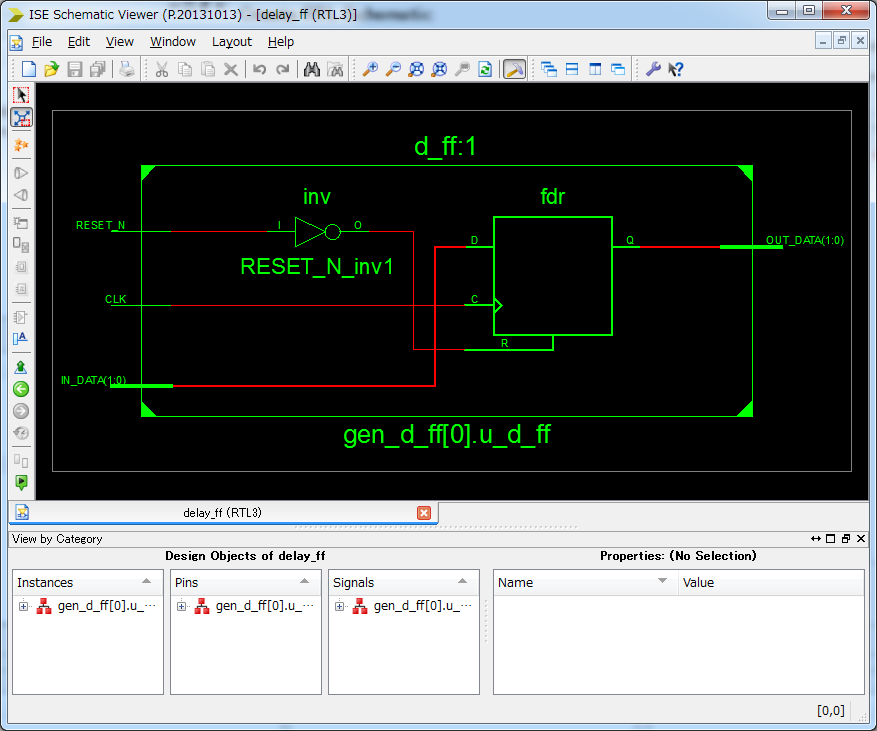

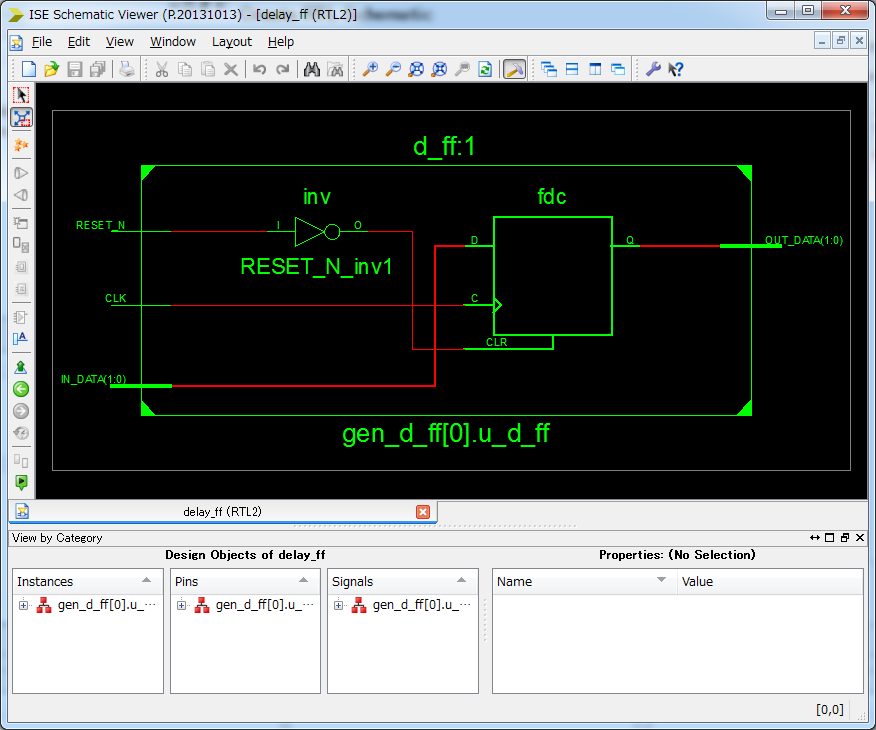

上記コードをSpartan-6にインプリメントしてみます。

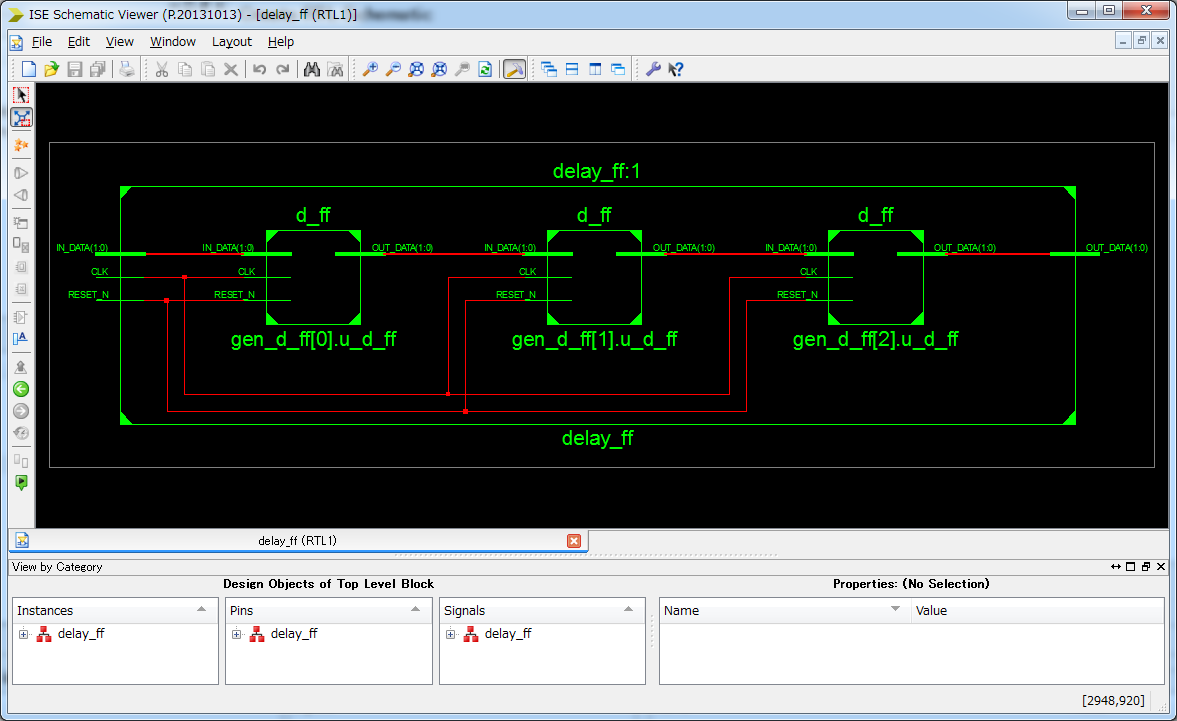

View RTL Schematic

IFF_USE = 0, OFF_USE = 0 の場合

IFF_USE = 1, OFF_USE = 0 の場合

IFF_USE = 0, OFF_USE = 1 の場合

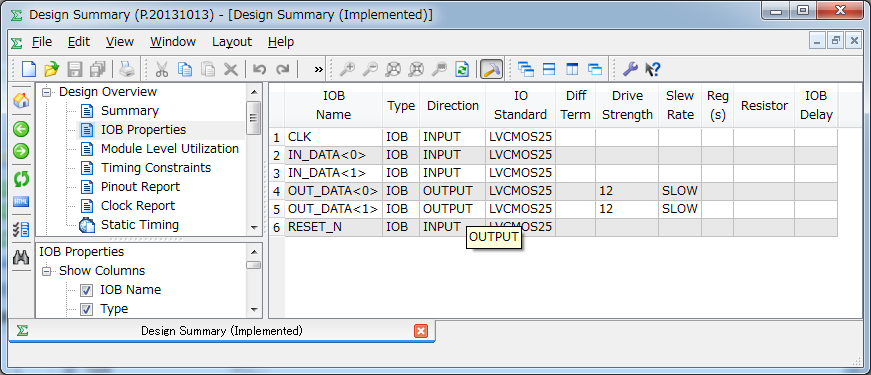

IOB propertiesのReg(s)欄を確認すると、IFFあるいはOFFが使用されています。

ARESET_USE = 0 (同期リセットの場合)

FDR : D Flip-Flop with Synchronous Reset

ARESET_USE = 1 (非同期リセットの場合)

FDC : D Flip-Flop with Asynchronous Clear