FastFETオペアンプAD8033を使った失敗事例③

作成者:mou-mou

今回は、FastFETオペアンプAD8033を使った失敗事例②の実回路での検証の結果を掲載いたします。

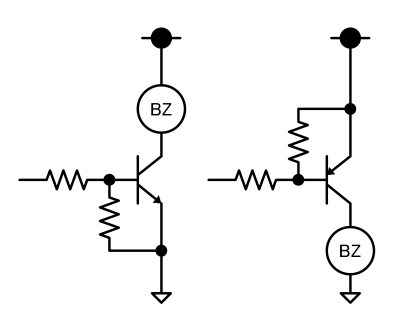

FastFETオペアンプAD8033を使った失敗事例①の回路からオペアンプをオンセミコンダクタ社製のCMOSオペアンプNCS2001SQ2T2Gに変更します。

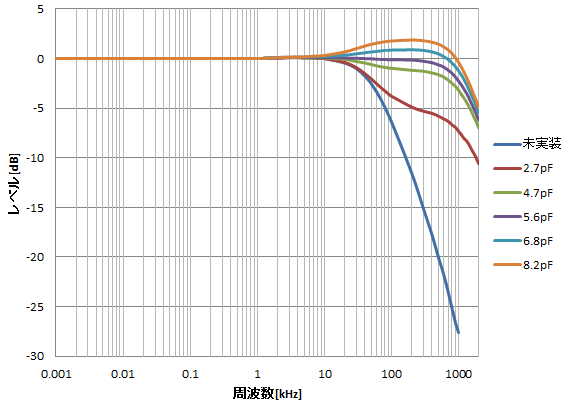

C4のコンデンサを実装しない時と数pFのコンデンサを実装した時のf-V特性を測定しました。

レベル[dB]は、1KHzの電圧値を0dBとしています。

シミュレーション結果と周波数軸にずれはありますが、傾向としては一致しています。

周波数特性保障用キャパシタを実装しない場合、100kHzで約6dB減衰しています。1MHzでは約27dB減衰しています。

では、周波数特性保障用キャパシタの値と特性を見てみると、シミュレーション結果では2.2pFあるいは2.7pFが良好な結果でしたが、実測では5.6pFが良好です。100kHzで約0.1dBの減衰、1MHzでは約2.3dBの減衰に抑えることが出来ました。

部品のバラツキの影響を抑えたい場合は、C4をトリマコンデンサにして100kHzで0dBとなるように調整すると良いのですが、今回は5.6pFの積層セラミックコンデンサに決定しました。

これで、今回の設計ミスから発生した問題は無事解決できました。

FastFETオペアンプという題目から脱線した解決方法となってしまいましたが、入力段にアッテネータ回路を実装した時の周波数特性の改善方法としてご参考にして頂けたらと思います。