Zybo Z7 Pcam 5C DemoをVivado 2020.02で動作させてみた

作成者:TZ

とある業務の動作検証として、Zybo Z7 Pcam 5C DemoをVivado 2020.02で実行したのですが、推奨バージョンの違いから何点か詰まる箇所がありましたので備忘録として残しておきます。

はじめに

環境

- Vivado 2020.02

- Pcam 5C Demo Zybo-Z7-20-pcam-5c-2019.1

準備

まずは下記のサイトで概要を確認します。

https://reference.digilentinc.com/learn/programmable-logic/tutorials/zybo-z7-pcam-5c-demo/start

GitHubよりReleaseのLatestを入手します。今回は記事作成時点でLatestのPcam 5C Demo Zybo-Z7-20-pcam-5c-2019.1を使用します。

https://github.com/Digilent/Zybo-Z7-20-pcam-5c?_ga=2.110380805.1080180363.1615162300-2030089044.1615013132

ダウンロードしたら任意のフォルダにzipを解答します。

環境構築の基本としてREADME.md(Zybo-Z7-20-pcam-5c-2019.1フォルダ内)を確認しましょう。構築方法が記載されておりますが2020.02とはメニュ構成が違うらしいので解釈しながら作業を進めていくことになります。

Vivado設定

Vitisへ渡すハードウェアデザインファイル(.xsa)を作成するための作業を行います。

プロジェクト起動

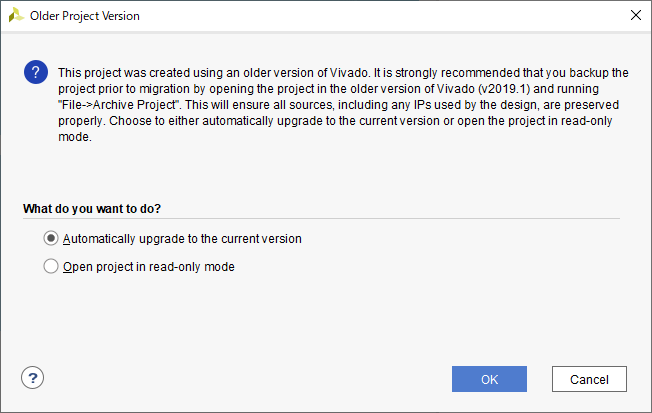

vivado_projフォルダ内のZybo-Z7-20-pcam-5c.xprをダブルクリックしVibadoを起動します。

Vivadoのバージョンのアップグレード確認なのでOKをクリックします。

Ignoreをクリックします。

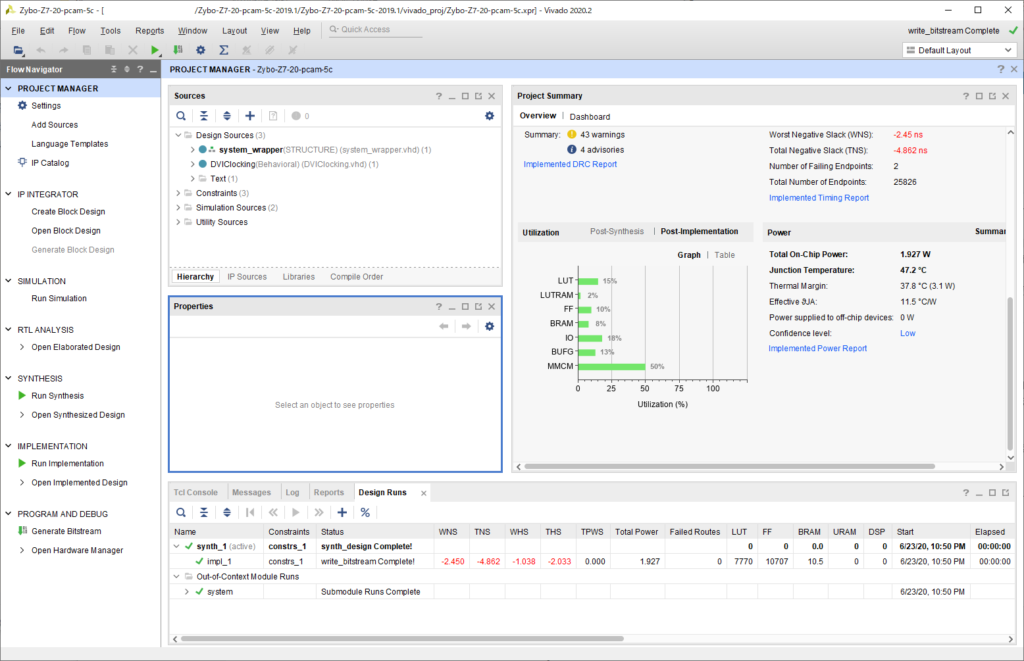

起動しました。

Bitstreamファイル(system_wrapper.bit)は、あらかじめ生成済のファイルがアーカイブ内に格納されているようですが、念のため[PROGRAM AND DEBUG] のGenerate Bitstreamを実行し更新します。

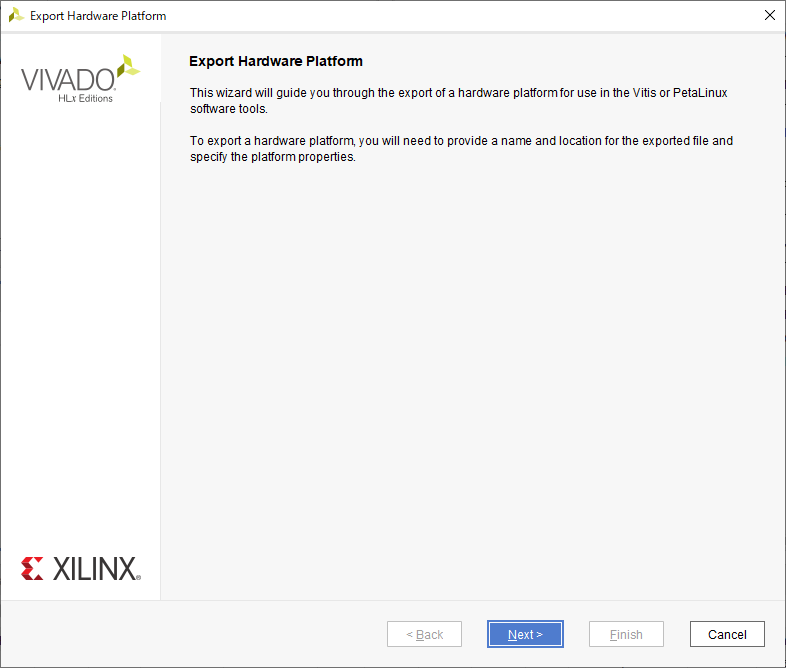

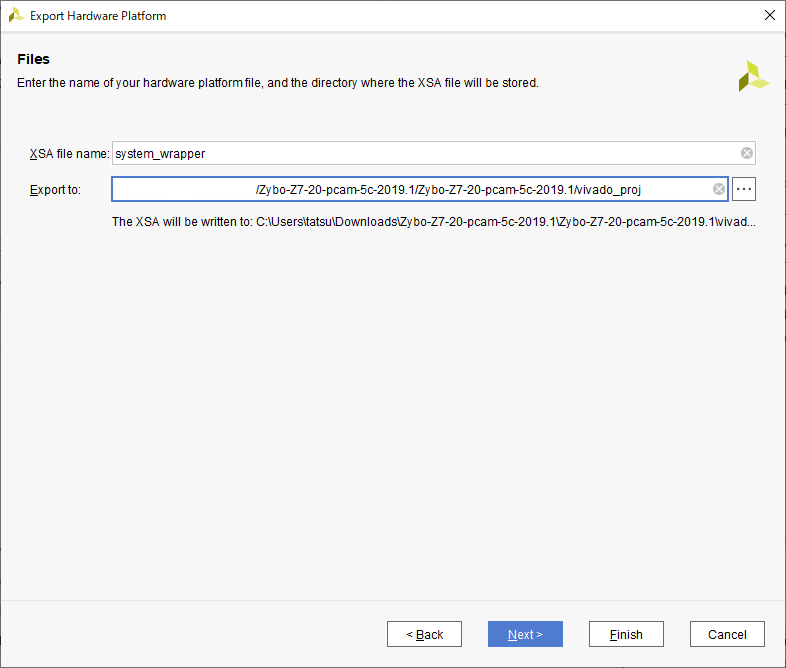

ハードウェアデザインファイル(.xsa)の作成

メニュから[File] -[Export] – [Export Hardware] を選択しNextをクリックします。

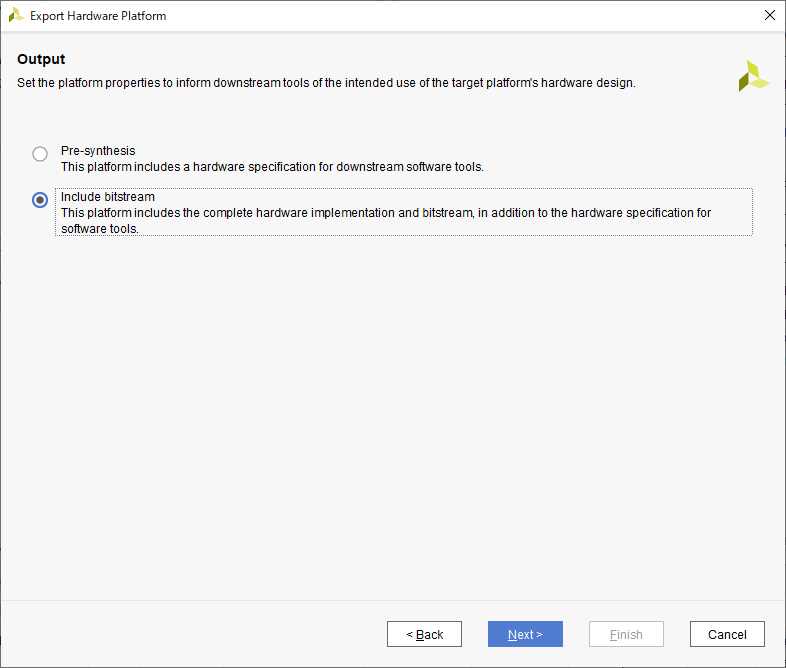

Include bitstreamを選択し、Nextをクリックします。

Exportフォルダがデフォルトから変更したい場合はExport Toを変更し、Next をクリックします。

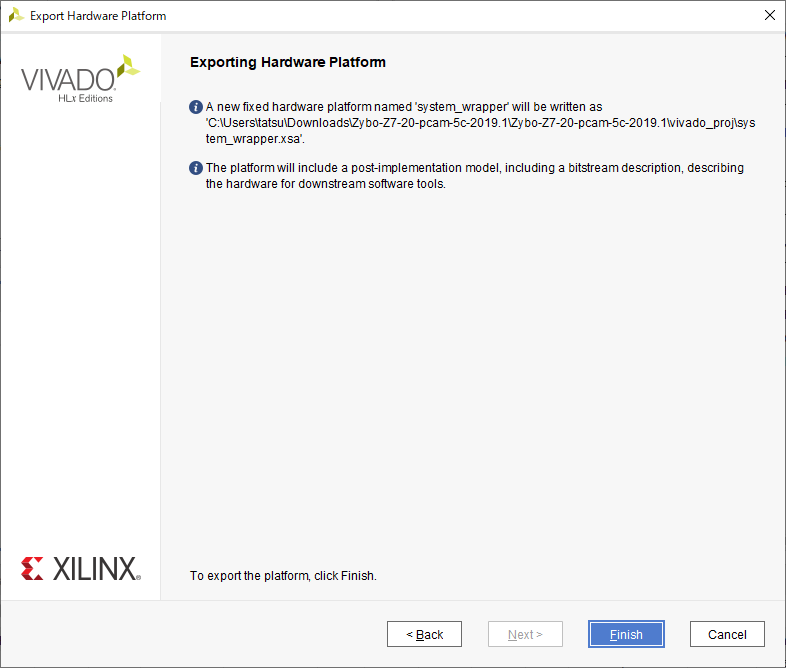

Finishをクリックします。

しばらく待つと、ハードウェアデザインファイルが指定されたフォルダにExportされます。

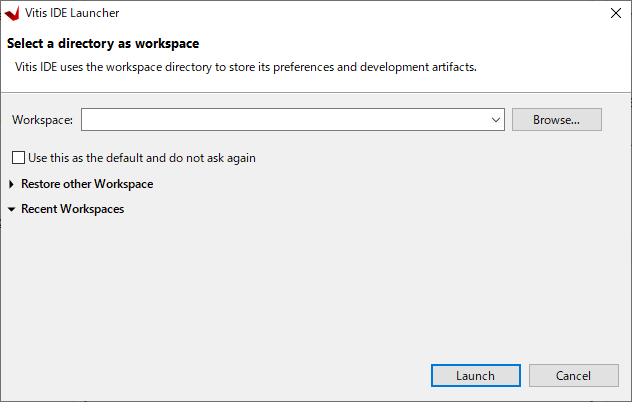

VivadoからVitisを起動する

メニュから[Tools] – [Launch Vitis IDE]を選択しVitis IDEを起動します。workspaceは任意の場所を選択しLaunchして下さい。

Vitis設定

まずはEmptyプロジェクトを作成

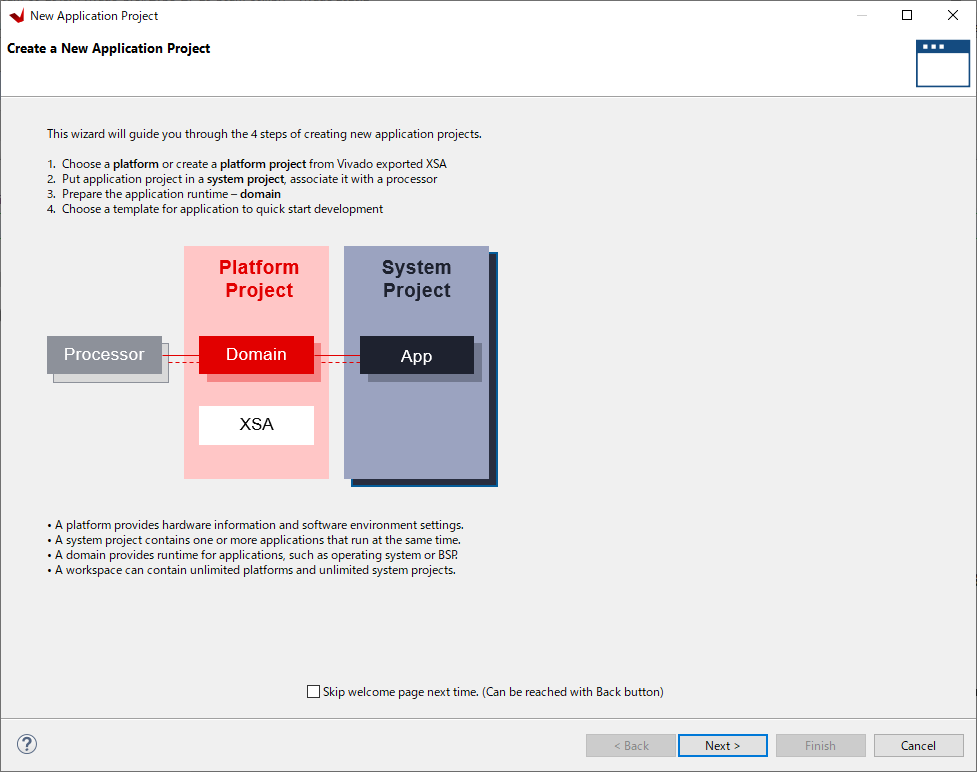

メニュから[File] – [New] – [Application Project]を選択します。

Nextをクリックします。

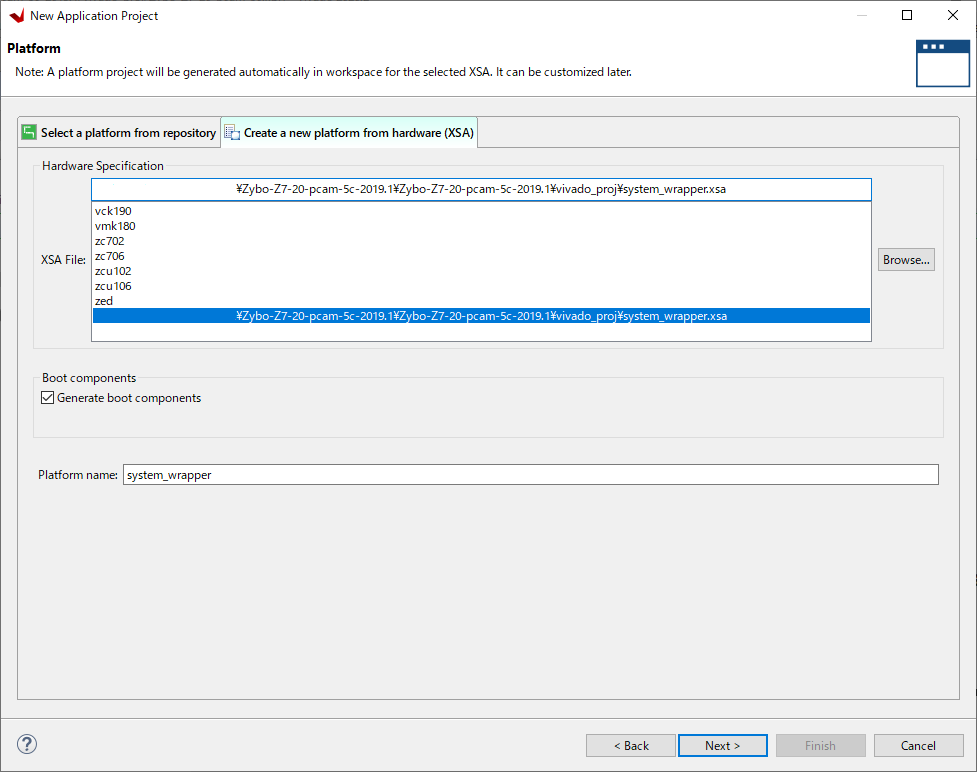

Create a new platform from hardware (XSA)タブを選択します。VivadoにてExportしたハードウェアデザインファイル(.XSA)を選択しNextをクリックします。

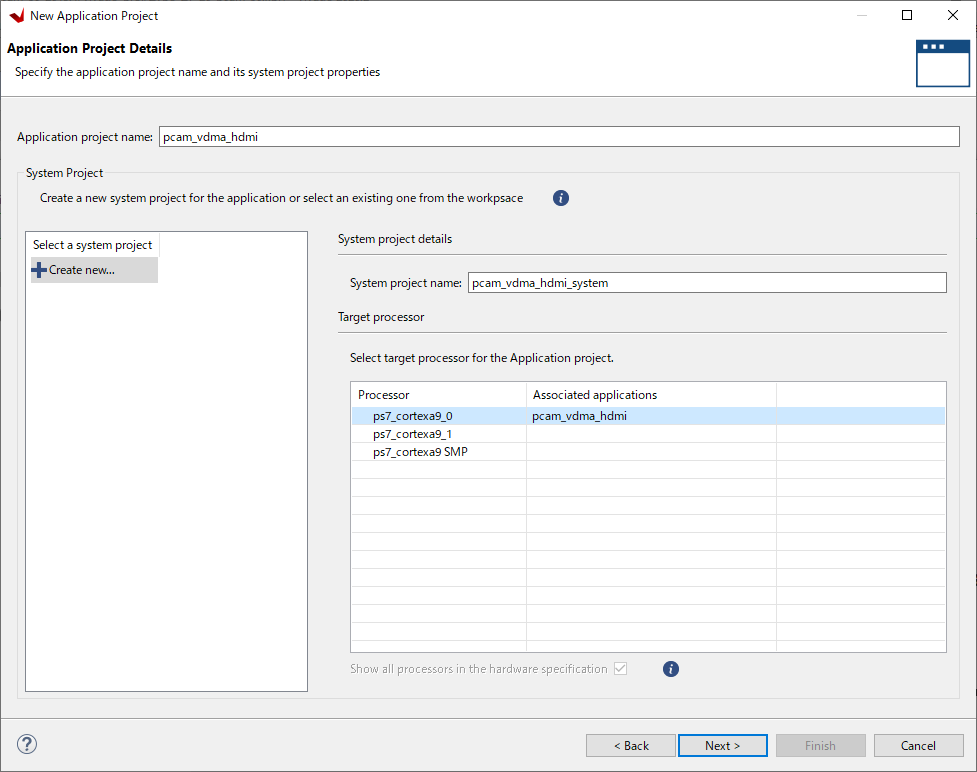

Application project nameを指定します。ここではREADME.mdに従いpcam_vdma_hdmiとしておくことにします。

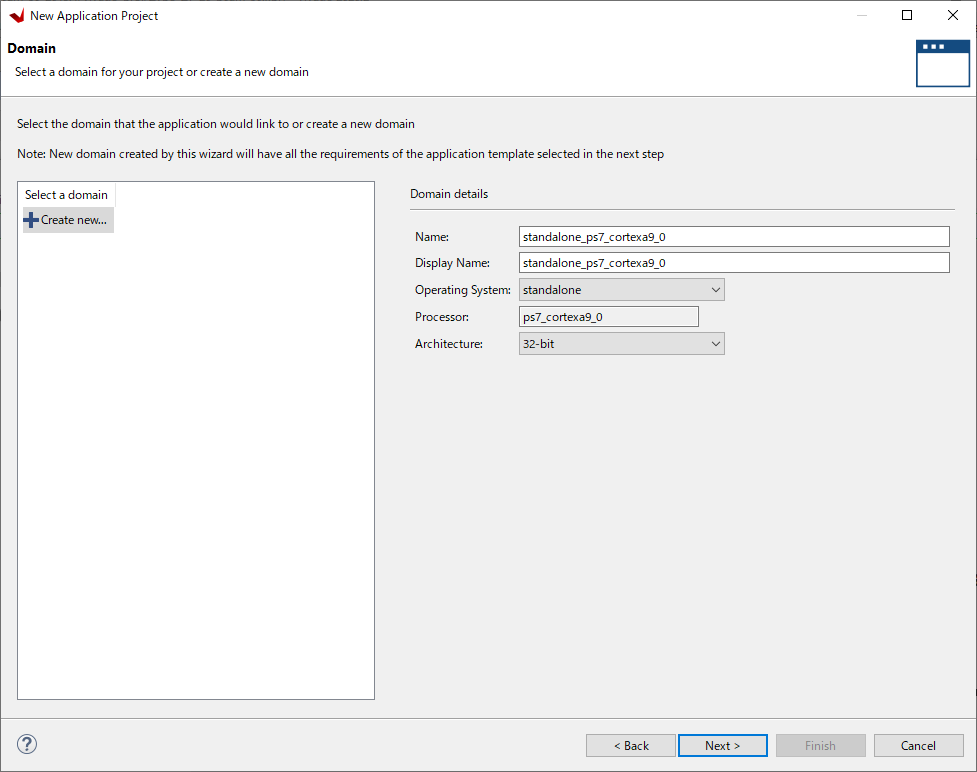

その後Nextをクリックします。

Nextをクリックします。

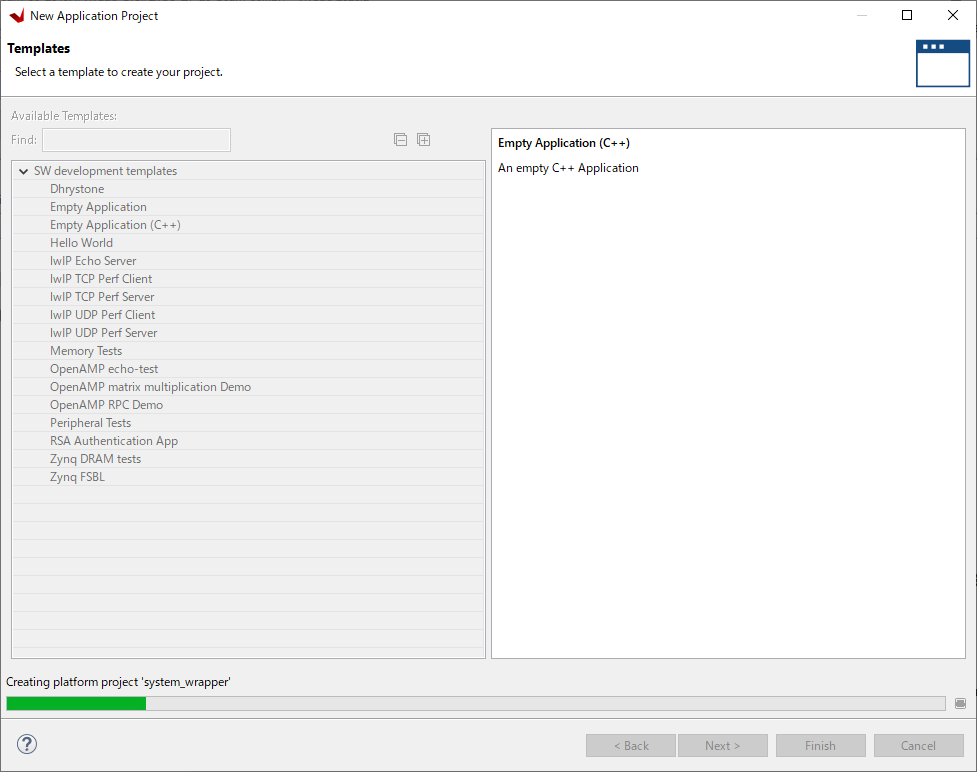

Empty Application (C++)を選択し、Finishをクリックします。

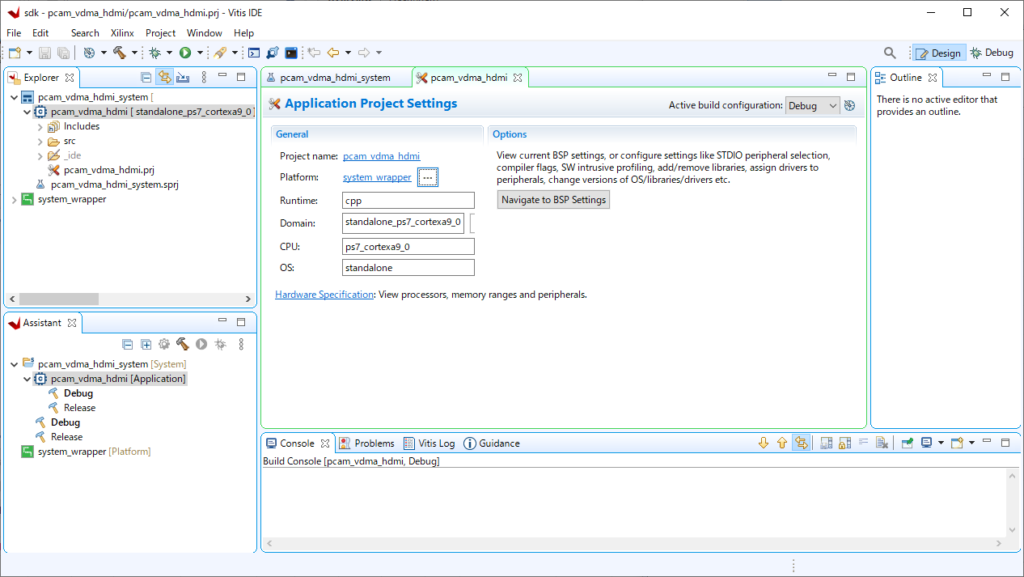

Emptyプロジェクトが作成できました。

sdk_appsrcをインポートする

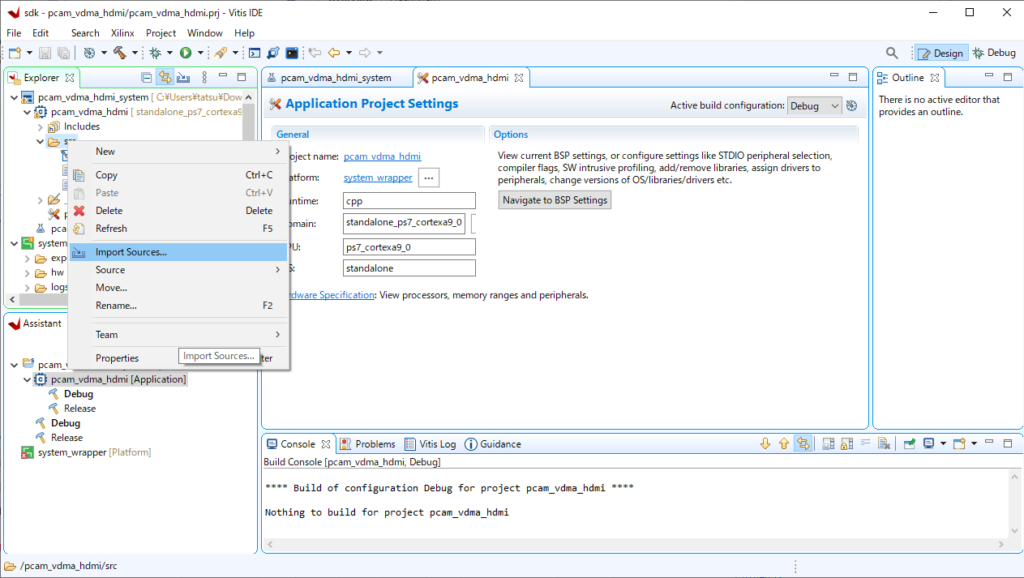

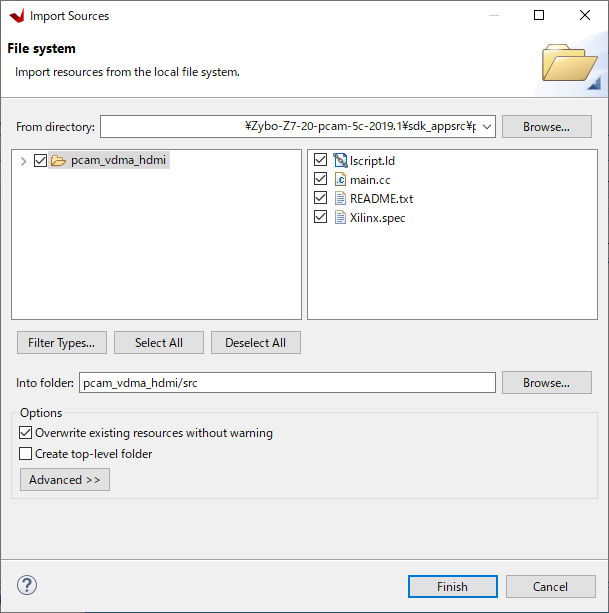

Explorerのpcam_vdma_hdmi_system/pcam_vdma_hdmi/srcにカーソルを合わせ右クリックし、Import Soruceを選択する。

From directoryに解凍したフォルダのsdk_appsrcを指定する。

README.mdに従い、

- pcam_vdma_hdmiをチェックする

- OptionのOverwrite existing resource without warningをチェックする

- Create top-level folderはチェックしない

インポートが完了しました。

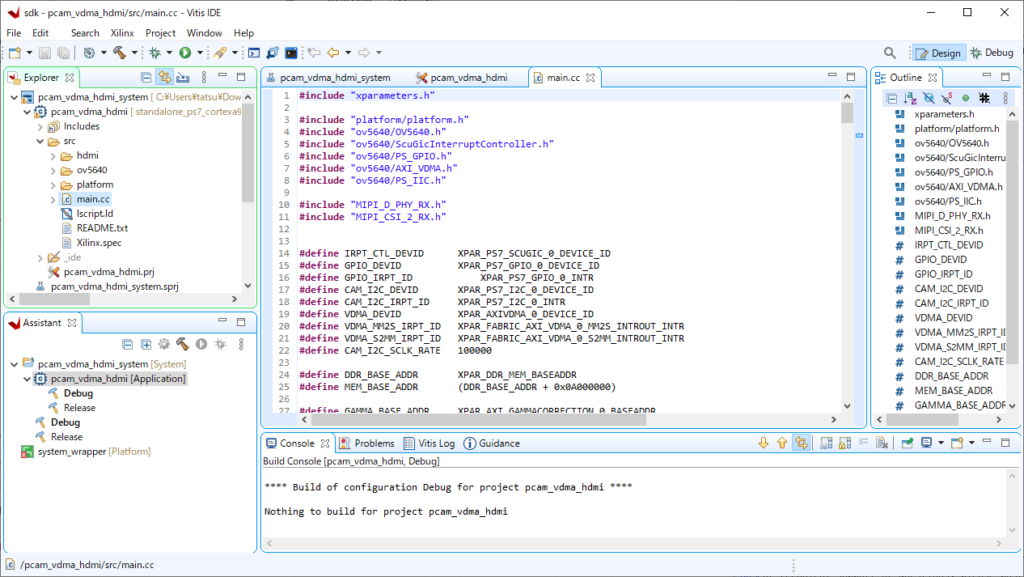

ビルドを実施

まずはsystem_wrapperをビルドしてみます。Explorerのsystem_wrapperを右クリックし [Build Project]を選択します。

しかし、ここでビルドエラーが発生しました。

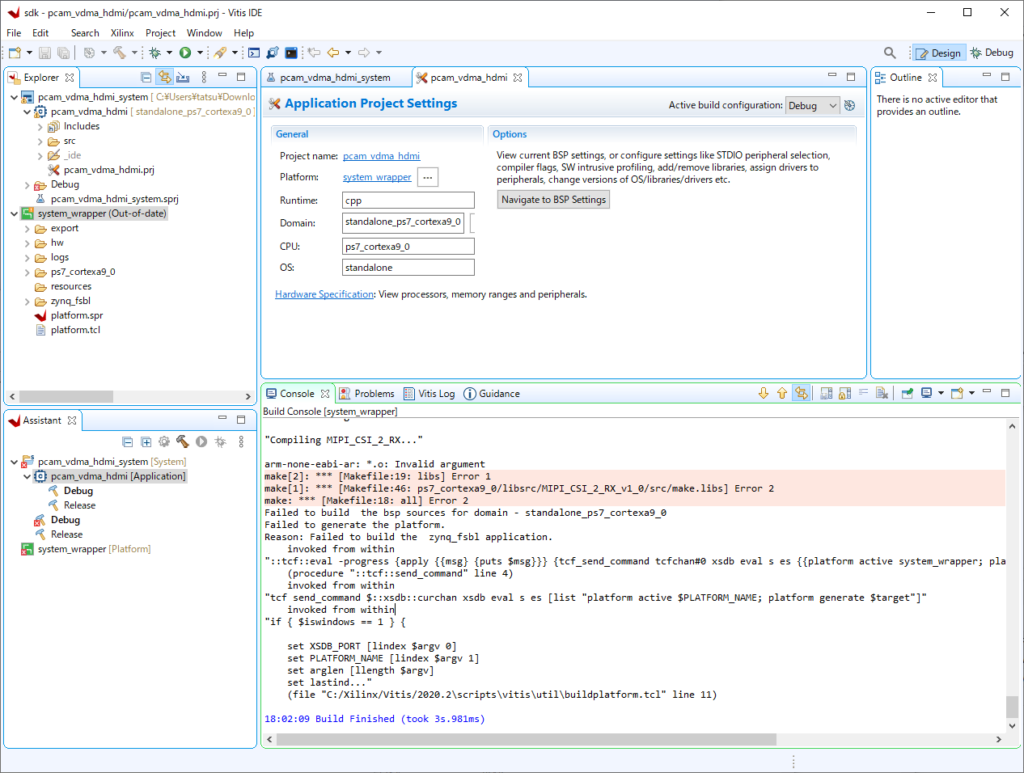

makefileを修正し再ビルド

エラー内容を抜粋し確認すると*.oの指定に問題がある事がわかります。どうやらVitis 2020.02を使ったことによるmake環境のバージョンの差異の問題のようです。

"Compiling MIPI_CSI_2_RX..."

arm-none-eabi-ar: *.o: Invalid argument

make[2]: *** [Makefile:19: libs] Error 1

make[1]: *** [Makefile:46: ps7_cortexa9_0/libsrc/MIPI_CSI_2_RX_v1_0/src/make.libs] Error 2

make: *** [Makefile:18: all] Error 2

make: Leaving directory 'sdk/system_wrapper/zynq_fsbl/zynq_fsbl_bsp'

"Compiling MIPI_CSI_2_RX..."

arm-none-eabi-ar: *.o: Invalid argument

make[2]: *** [Makefile:19: libs] Error 1

make[1]: *** [Makefile:46: ps7_cortexa9_0/libsrc/MIPI_CSI_2_RX_v1_0/src/make.libs] Error 2

make: *** [Makefile:18: all] Error 2

Failed to build the bsp sources for domain - standalone_ps7_cortexa9_0

Failed to generate the platform.

Reason: Failed to build the zynq_fsbl application.

invoked from within

"::tcf::eval -progress {apply {{msg} {puts $msg}}} {tcf_send_command tcfchan#0 xsdb eval s es {{platform active system_wrapper; platform generate }}}"

(procedure "::tcf::send_command" line 4)

invoked from within

"tcf send_command $::xsdb::curchan xsdb eval s es [list "platform active $PLATFORM_NAME; platform generate $target"]"

invoked from within

"if { $iswindows == 1 } {

set XSDB_PORT [lindex $argv 0]

set PLATFORM_NAME [lindex $argv 1]

set arglen [llength $argv]

set lastind..."

(file "C:/Xilinx/Vitis/2020.2\scripts\vitis\util\buildplatform.tcl" line 11)

17:58:51 Build Finished (took 3s.929ms)この内容を調査すると以下のフォーラムに解決策が投稿されておりました。

https://forum.digilentinc.com/topic/20756-error-compiling-pmodgyro/

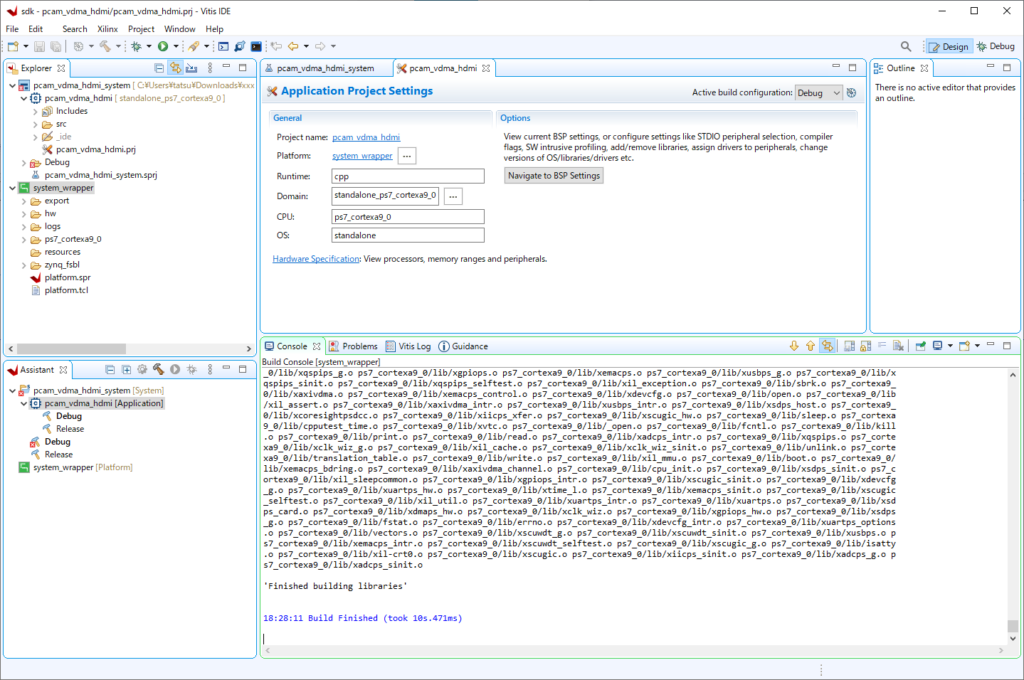

結論としてはmakefileのOUTSの記述を修正する必要があります。元のOUTSの定義をコメント化し下記のように定義します。

#OUTS = *.o

OUTS = $(addsuffix .o, $(basename $(wildcard *.c)))修正するmakefileはVitisプロジェクト内を検索すると、下記の6か所がヒットしますので全て書き換えておきます。

system_wrapper\hw\drivers\MIPI_CSI_2_RX_v1_0\src\Makefile(14,1) [UTF-8]: OUTS = *.o

system_wrapper\hw\drivers\MIPI_D_PHY_RX_v1_0\src\Makefile(14,1) [UTF-8]: OUTS = *.o

system_wrapper\ps7_cortexa9_0\standalone_ps7_cortexa9_0\bsp\ps7_cortexa9_0\libsrc\MIPI_CSI_2_RX_v1_0\src\Makefile(14,1) [UTF-8]: OUTS = *.o

system_wrapper\ps7_cortexa9_0\standalone_ps7_cortexa9_0\bsp\ps7_cortexa9_0\libsrc\MIPI_D_PHY_RX_v1_0\src\Makefile(14,1) [UTF-8]: OUTS = *.o

system_wrapper\zynq_fsbl\zynq_fsbl_bsp\ps7_cortexa9_0\libsrc\MIPI_CSI_2_RX_v1_0\src\Makefile(14,1) [UTF-8]: OUTS = *.o

system_wrapper\zynq_fsbl\zynq_fsbl_bsp\ps7_cortexa9_0\libsrc\MIPI_D_PHY_RX_v1_0\src\Makefile(14,1) [UTF-8]: OUTS = *.o

makefile修正後、再度ビルドすると成功することが確認できました。

あとはpcam_vdma_hdmiプロジェクトをビルドし、pcam_vdma_hdmi.elfが出力されればビルド作業は完了です。

実機確認

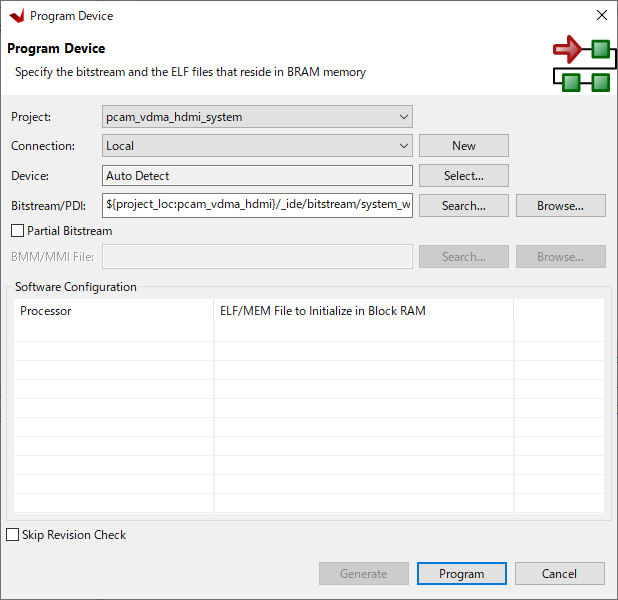

メニューから[Xilinx] – [Program Device] を選択し、 [Prrogram]をクリックしProgrammable Logicを転送しておく。

その後、デバッグの開始等でProcessing Systemを転送し実行開始。

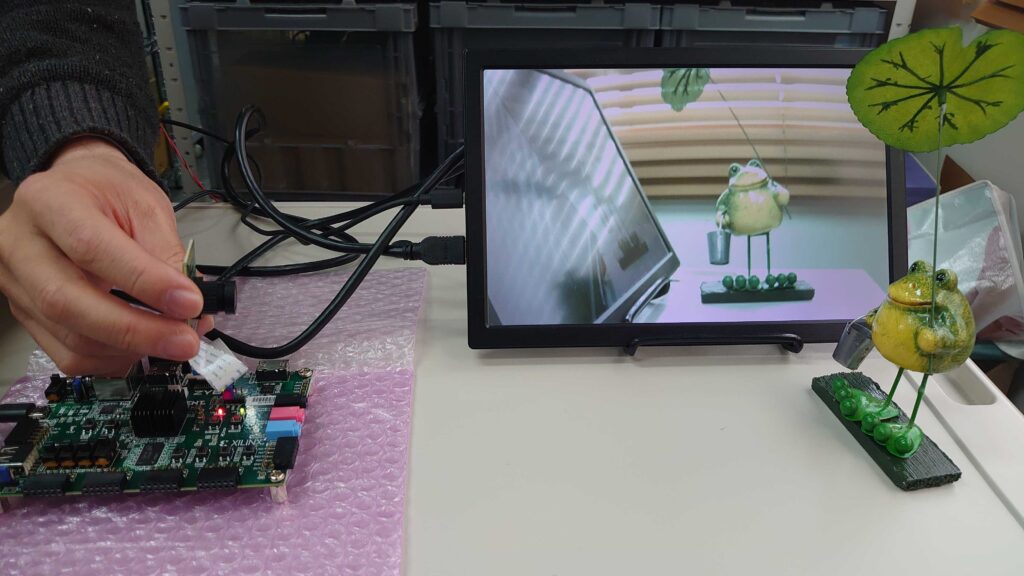

カメラ画像がHDMI出力されていることが確認できました。