Pericallis ユニバーサルテスタ

ユニバーサルテスタのプロトタイプ機です。 信号発生器と信号モニタの機能を有した汎用テスタです。ソフトウエアのカスタマイズによって研究開発や工程検査のツールとして使用できます。

| CPU |

AP4010 / ARM926EJ-S

|

| クロック |

CPUコア 108MHz / バスクロック 108MHz

|

| ROM |

NOR FLASH 4Mbyte, NAND FLASH 32Mbyte

|

| RAM |

SDRAM 32Mbyte, SRAM 2Mbyte x2

|

| OS |

TOPPERS JSP(μITRON4.0仕様準拠)

|

| LCD |

6.4inch TFT VGA (640×480ピクセル)

|

| タッチパネル |

4線式 抵抗膜方式

|

| ネットワーク |

10Base-TX(TCP/IP, Telnet, FTP)

|

| FPGA |

Spartan3E X2 (XC3S250E, XC3S500E 各1chip

|

| アナログ入力 |

2ch, 40Msps, 入力電圧範囲±40V

|

| デジタル入力 |

2ch, 40Msps, 入力電圧範囲1.8~5V

|

| アナログ出力 |

2ch, 40Msps, 出力電圧範囲±4V

|

| デジタル出力 |

2ch, 40Msps, 出力電圧範囲1.8~5V

|

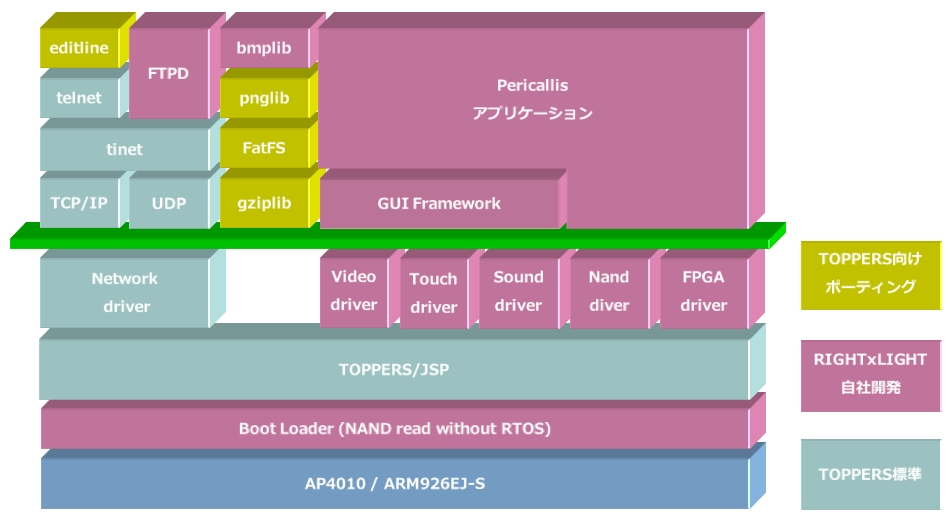

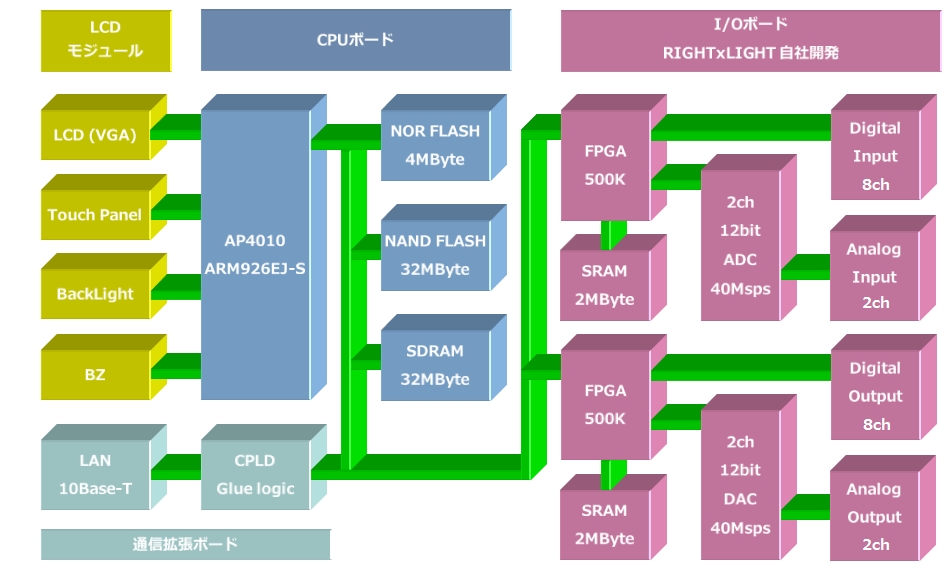

Pericallisユニバーサルテスタのソフトウエアとハードウエアの構成を下図に示します。

ソフトウエア構成図は、TOPPERS標準と弊社にてポーティングした部分、自社開発した部分を色別で記載しております。ハードウエア構成図は、ボード・モジュール構成を色別で記載しております。